New ARM Interconnect Technology Addresses Demand for 'Many-core' Solutions

ARM has announced the ARM CoreLink CCN-504 cache coherent network, a system intellectual property (IP) that can deliver up to one terabit of usable system bandwidth per second.

ARM expects the new system to enable SoC designers to provide high-performance, cache coherent interconnect for 'many-core' enterprise solutions built using the ARM Cortex-A15 MPCore processor and next-generation 64-bit processors.

ARM said that LSI and Calxeda were among the licensees for the CoreLink CCN-504 launch.

ARM has also unveiled the new ARM CoreLink DMC-520 dynamic memory controller that has been designed and optimized to work with the CoreLink CCN-504. The new dynamic memory controller provides a high-bandwidth interface to shared off-chip memory, such as DDR3, DDR3L and DDR4 DRAM. It is part of an integrated ARM DDR4 interface solution incorporating ARM Artisan DDR4/3 PHY IP planned for introduction in 2013.

CoreLink CCN-504 enables a many-core solution that supports up to 16 cores on the same silicon die. It enables system coherency in heterogeneous multicore and multi-cluster CPU/GPU systems by enabling each processor in the system to access the other processor caches. This reduces the need to access off-chip memory, saving time and energy, which is a key enabler in systems based on ARM big.LITTLE processing.

"As the amount of data used increases exponentially over the next 10-15 years, the CoreLink CCN-504 and DMC-520 will play an important role by providing high-performance system IP solutions for many-core applications," said Tom Cronk, deputy general manager, processor division, ARM. "This ensures quality of service and coherent operation across the system, and enables SoC designers to efficiently prioritize and handle wide data flows with optimum latency."

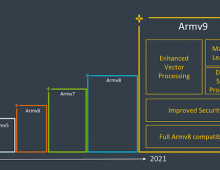

The CoreLink CCN-504 supports both the current-generation Cortex-A15 processor and future ARMv8 processors and is the first in a family of network-based interconnect products planned by ARM.

The CoreLink CCN-504 cache coherent network includes integrated level 3 (L3) cache and snoop filter functions. The L3 cache, which is configurable up to 16MB, extends on-chip caching for demanding workloads and offers low latency on-chip memory for allocation and sharing of data between processors, high-speed IO interfaces and accelerators. The snoop filter removes the need for broadcast coherency messaging, further reducing latency and power.

The ARM CoreLink CCN-504 cache coherent network is available to licensees now, and sampling in products in 2013.

ARM said that LSI and Calxeda were among the licensees for the CoreLink CCN-504 launch.

ARM has also unveiled the new ARM CoreLink DMC-520 dynamic memory controller that has been designed and optimized to work with the CoreLink CCN-504. The new dynamic memory controller provides a high-bandwidth interface to shared off-chip memory, such as DDR3, DDR3L and DDR4 DRAM. It is part of an integrated ARM DDR4 interface solution incorporating ARM Artisan DDR4/3 PHY IP planned for introduction in 2013.

CoreLink CCN-504 enables a many-core solution that supports up to 16 cores on the same silicon die. It enables system coherency in heterogeneous multicore and multi-cluster CPU/GPU systems by enabling each processor in the system to access the other processor caches. This reduces the need to access off-chip memory, saving time and energy, which is a key enabler in systems based on ARM big.LITTLE processing.

"As the amount of data used increases exponentially over the next 10-15 years, the CoreLink CCN-504 and DMC-520 will play an important role by providing high-performance system IP solutions for many-core applications," said Tom Cronk, deputy general manager, processor division, ARM. "This ensures quality of service and coherent operation across the system, and enables SoC designers to efficiently prioritize and handle wide data flows with optimum latency."

The CoreLink CCN-504 supports both the current-generation Cortex-A15 processor and future ARMv8 processors and is the first in a family of network-based interconnect products planned by ARM.

The CoreLink CCN-504 cache coherent network includes integrated level 3 (L3) cache and snoop filter functions. The L3 cache, which is configurable up to 16MB, extends on-chip caching for demanding workloads and offers low latency on-chip memory for allocation and sharing of data between processors, high-speed IO interfaces and accelerators. The snoop filter removes the need for broadcast coherency messaging, further reducing latency and power.

The ARM CoreLink CCN-504 cache coherent network is available to licensees now, and sampling in products in 2013.