Intel Launches Agilex 7 FPGAs with R-Tile, First FPGA with PCIe 5.0 and CXL Capabilities

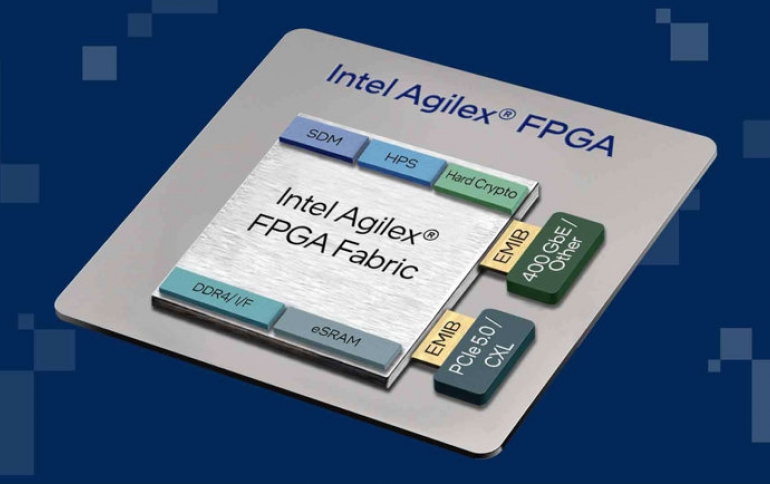

Intel’s Programmable Solutions Group today announced that the Intel Agilex® 7 with the R-Tile chiplet is shipping production-qualified devices in volume – bringing customers the first FPGA with PCIe 5.0 and CXL capabilities and the only FPGA with hard intellectual property (IP) supporting these interfaces.

“Customers are demanding cutting-edge technology that offers the scalability and customization needed to not only efficiently manage current workloads, but also pivot capabilities and functions as their needs evolve. Our Agilex products offer the programmable innovation with the speed, power and capabilities our customers need while providing flexibility and resilience for the future. For example, customers are leveraging R-Tile, with PCIe Gen 5 and CXL, to accelerate software and data analytics, cutting the processing time from hours to minutes.” –Shannon Poulin, Intel corporate vice president and general manager of the Programmable Solutions Group

How It Works: Agilex 7 FPGAs with the R-Tile chiplet deliver leading technology capabilities with 2-times faster PCIe 5.0 bandwidth as well as 4-times higher CXL bandwidth per port when compared to other competitive FPGA products. According to a white paper from Meta and the University of Michigan, adding FPGAs with CXL memory to 4th Gen Xeon-based servers while using transparent page placement’s (TPP) efficient page placement improves Linux performance by up to 18%. Additionally, UnifabriX demonstrated its CXL-enabled Smart Memory Node on multiple performance benchmarks, with one showing a 28% increase in the HPCG (high-performance conjugate gradient) benchmark score while utilizing 2-times more 4th Gen Xeon cores for HPC workloads.

More Context: To learn more about the product or how to purchase, check out the blog for additional details.