ISSCC: Intel Presents 2.5D FPGA, AMD Details Upcoming Zen x86 Core

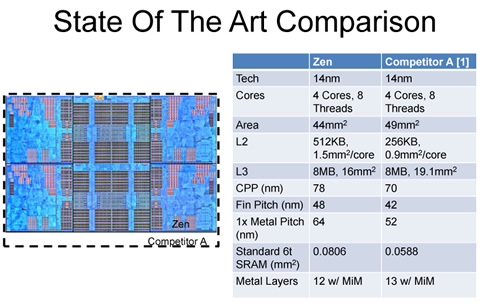

Intel provided a detailed look at its lower cost alternative to 2.5D packaging in a paper on its Stratix X FPGA, while AMD showed its Zen x86 processor sports a 10 percent smaller die than Intel's latest 14nm CPUs.

The presentations were made at the International Solid State Circuits Conference (ISSCC) in San Franscisco.

The Stratix X uses Intel's Embedded Multi-die Interconnect Bridge (EMIB) to link the FPGA with four external transceivers. The bridge is made using silicon die mounted in a BGA substrate which is significantly smaller than the silicon substrates used in the CoWoS process developed by TSMC and used by rival FPGA vendor Xilinx and GPU designer Nvidia.

EMIB uses a combination of 55 micron micro-bumps and 100+ micron flip-chip bumps to support up to 24 transceiver channels with 96 I/Os each. They deliver 2 Gbits/second/pin at 1.2 pJ/bit/die using a proprietary protocol.

Currently, the bridge links four 28 GHz serdes to the FPGA. Intel has a road map to faster serdes and other kinds of external chips.

Intel said it doesn't foresee any issues dealing with thermal challenges migrating the design to 56G serdes.

Intel is offering the technology in its foundry service. So far, it has not announced any other users of EMIB. The 14nm Stratix X packs 2.8 million logic elements into a 560mm2 fabric running at a gigahertz.

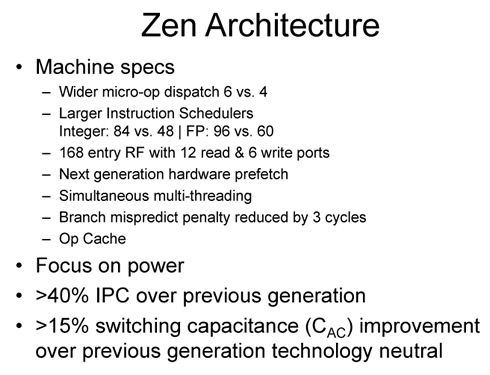

Seperately, AMD said its upcoming Zen x86 core fits into a 10 percent smaller die area than Intel's currently shipping second-generation 14nm processor.

The paper detailed techniques AMD used to reduce switching capacitance by 15 percent compared to its existing chips. For example, Zen marked AMD's first use of a metal-insulator-metal capacitor which helped lower operating voltages and provide greater per-core voltage and frequency control.

Engineers tracked on a weekly basis power benchmarks on high activity regions for more than a year to reduce switching capacitance. The company now has two eight-core designs running with simultaneous multithreading at 3.4 GHz.