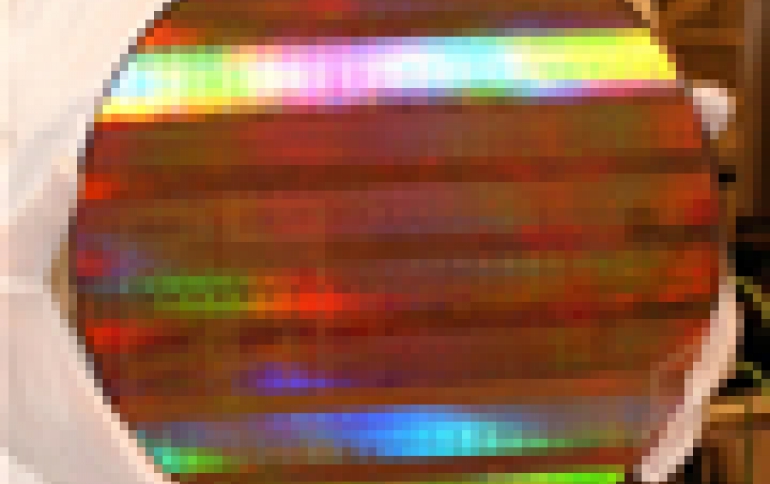

TSMC To Delay Transition To 450-mm Wafers

Taiwan Semiconductor Manufacturing Co. (TSMC) will start

using 450-millimeter wafers to build its processors in

2018, following delays in the development of the new

technology.

J.K. Wang, Taiwan Semiconductor Manufacturing Co.?s vice

president for operations/300mm fabs, said the company will

begin volume production of chips on 450mm silicon wafers in

2018, offering FinFET transistor technology at 10nm node.

He noted that TSMC has completed its planning for deploying

450mm wafer production.

The company's vice president for research and development, Burn Lin, pointed out that TSMC will begin volume production of FinFET transistors at 20nm process and is on the track to deploy 16nm FinFET process. In addition to ultraviolet lithography, Lin said that TSMC is also considering multi e-beam lithography technology for its 10nm FinFET process. He pointed out that TSMC will use the legacy immersion lithography technology on its 10nm and 16nm transistors as EUV is still immature. However, transistors smaller than 10nm will use next-generation lithography technology.

Intel, TSMC, Samsung, IBM, and GlobalFoundry have formed an alliance to push for 450mm technology.

Currently, chip makers are using silicon wafers at the 300-mm size to build their processors. Upgrading to the 450-mm level would allow companies to produce more chips from each wafer, as the 450-mm wafers have 2.5 times more surface area.

Industry has been slow to move forward to 450-mm wafer manufacturing, as billions of dollars are needed to invest in building the tools and factories to produce the wafers.

The company's vice president for research and development, Burn Lin, pointed out that TSMC will begin volume production of FinFET transistors at 20nm process and is on the track to deploy 16nm FinFET process. In addition to ultraviolet lithography, Lin said that TSMC is also considering multi e-beam lithography technology for its 10nm FinFET process. He pointed out that TSMC will use the legacy immersion lithography technology on its 10nm and 16nm transistors as EUV is still immature. However, transistors smaller than 10nm will use next-generation lithography technology.

Intel, TSMC, Samsung, IBM, and GlobalFoundry have formed an alliance to push for 450mm technology.

Currently, chip makers are using silicon wafers at the 300-mm size to build their processors. Upgrading to the 450-mm level would allow companies to produce more chips from each wafer, as the 450-mm wafers have 2.5 times more surface area.

Industry has been slow to move forward to 450-mm wafer manufacturing, as billions of dollars are needed to invest in building the tools and factories to produce the wafers.