AMD Uses New Low-power Clock IP

AMD has implemented Cyclos' low-power semiconductor intellectual property (IP) in the AMD x86 core destined for inclusion in Opteron server processors and client Accelerated Processing Units (APUs).

Cyclos Semiconductor is the inventor and only supplier of resonant clock mesh technology for commercial IC designs.

At the International Solid State Circuits Conference (ISSCC) in San Francisco, the company announced that AMD licensed its technology to reduce power consumption of APUs.

AMD's 4+ GHz x86-64 core code-named "Piledriver" employs resonant clocking to reduce clock distribution power up to 24% while maintaining the low clock-skew target required by high-performance processors. Fabricated in a 32nm CMOS process, Piledriver represents the first volume production-enabled implementation of resonant clock mesh technology.

"We were able to seamlessly integrate the Cyclos IP into our existing clock mesh design process so there was no risk to our development schedule.", said Samuel Naffziger, Corporate Fellow at AMD. "Silicon results met our power reduction expectations, we incurred no increase in silicon area, and we were able to use our standard manufacturing process, so the investment and risk in adopting resonant clock mesh technology was well worth it as all of our customers are clamoring for more energy efficient processor designs."

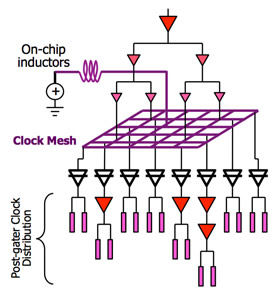

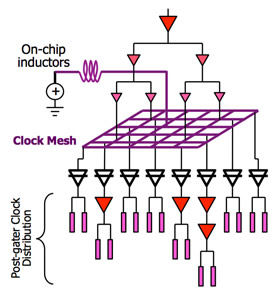

Cyclos resonant clock mesh technology employs on-chip inductors to create an electric pendulum, or "tank circuit", formed by the large capacitance of the clock mesh in parallel with the Cyclos inductors. The Cyclos inductors and clock control circuits "recycle" the clock power instead of dissipating it on every clock cycle like in a clock tree implementation, which results in a reduction in total IC power consumption of up to 10%.

Cyclos resonant clock mesh technology employs on-chip inductors to create an electric pendulum, or "tank circuit", formed by the large capacitance of the clock mesh in parallel with the Cyclos inductors. The Cyclos inductors and clock control circuits "recycle" the clock power instead of dissipating it on every clock cycle like in a clock tree implementation, which results in a reduction in total IC power consumption of up to 10%.

"High-performance processors have used clock mesh designs for years, but with growing emphasis on power reduction in both servers and mobile PCs, the traditional approach has become too power hungry," said Linley Gwennap, principal analyst of The Linley Group. "This announcement proves that the Cyclos resonant clock mesh technology provides meaningful power savings in real-world products. We expect other processor designers to adopt the Cyclos technology in applications where power reduction is important."

Implementing inductors on-chip to resonate a clock mesh is a simple idea with complex implementation requirements. Cyclos has commercialized over 10 years of research to produce the first resonant clock mesh design solution that meets all the testability, reliability, dynamic frequency scaling, and quality assurance requirements of today's ICs. "This is a major milestone for Cyclos Semiconductor.", said Marios Papaefthymiou, founder and President of Cyclos Semiconductor. "Now that the Cyclos technology is validated, we're looking forward to expand into SoC designs via the design automation tools that are in development at Cyclos. We believe resonant clock mesh design will be a key enabler for GHz+ embedded processor IP blocks in next generation SoCs that also require ultra-low power consumption."

At the International Solid State Circuits Conference (ISSCC) in San Francisco, the company announced that AMD licensed its technology to reduce power consumption of APUs.

AMD's 4+ GHz x86-64 core code-named "Piledriver" employs resonant clocking to reduce clock distribution power up to 24% while maintaining the low clock-skew target required by high-performance processors. Fabricated in a 32nm CMOS process, Piledriver represents the first volume production-enabled implementation of resonant clock mesh technology.

"We were able to seamlessly integrate the Cyclos IP into our existing clock mesh design process so there was no risk to our development schedule.", said Samuel Naffziger, Corporate Fellow at AMD. "Silicon results met our power reduction expectations, we incurred no increase in silicon area, and we were able to use our standard manufacturing process, so the investment and risk in adopting resonant clock mesh technology was well worth it as all of our customers are clamoring for more energy efficient processor designs."

Cyclos resonant clock mesh technology employs on-chip inductors to create an electric pendulum, or "tank circuit", formed by the large capacitance of the clock mesh in parallel with the Cyclos inductors. The Cyclos inductors and clock control circuits "recycle" the clock power instead of dissipating it on every clock cycle like in a clock tree implementation, which results in a reduction in total IC power consumption of up to 10%.

Cyclos resonant clock mesh technology employs on-chip inductors to create an electric pendulum, or "tank circuit", formed by the large capacitance of the clock mesh in parallel with the Cyclos inductors. The Cyclos inductors and clock control circuits "recycle" the clock power instead of dissipating it on every clock cycle like in a clock tree implementation, which results in a reduction in total IC power consumption of up to 10%.

"High-performance processors have used clock mesh designs for years, but with growing emphasis on power reduction in both servers and mobile PCs, the traditional approach has become too power hungry," said Linley Gwennap, principal analyst of The Linley Group. "This announcement proves that the Cyclos resonant clock mesh technology provides meaningful power savings in real-world products. We expect other processor designers to adopt the Cyclos technology in applications where power reduction is important."

Implementing inductors on-chip to resonate a clock mesh is a simple idea with complex implementation requirements. Cyclos has commercialized over 10 years of research to produce the first resonant clock mesh design solution that meets all the testability, reliability, dynamic frequency scaling, and quality assurance requirements of today's ICs. "This is a major milestone for Cyclos Semiconductor.", said Marios Papaefthymiou, founder and President of Cyclos Semiconductor. "Now that the Cyclos technology is validated, we're looking forward to expand into SoC designs via the design automation tools that are in development at Cyclos. We believe resonant clock mesh design will be a key enabler for GHz+ embedded processor IP blocks in next generation SoCs that also require ultra-low power consumption."