Infineon and Nanya Announce Mass Production of 90nm DRAM

Infineon Technologies AG and Nanya Technology Corporation yesterday announced the successful

qualification of 90nm DRAM technology which was jointly developed at Infineon?s Research Center in

Dresden, Germany.

Both companies have already qualified the 90nm memory products at major customers and achieved

validation of Intel. DRAM volume production with 90nm process structures on 300mm has first started at

Infineon?s 300mm production line in Dresden. Being the second DRAM manufacturer worldwide introducing

90nm technology, Infineon has already converted by end of May around 5 percent of its total global DRAM

production from 110nm to 90nm. Inotera Memories, the Taiwan-based manufacturing joint venture of Infineon

and Nanya is starting the 90nm transition now. Early adoption of the next generation technology node

allows to significantly improve production costs and product performances and is one of the most important

factors to increase profitability in DRAM manufacturing.

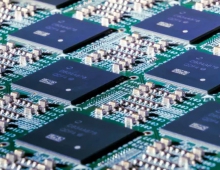

Process structures of 90nm further reduce chip size compared to the previous 110nm technology thereby increasing potential chip output per wafer by more than 30 percent. The expected productivity increase by shrinking the chip size combined with the use of 300mm wafers is the basis for a significant reduction of production cost per chip. The strategic development alliance of Infineon and Nanya also covers the next technology node with 70nm structures.

Except for its cost advantage, transition to smaller process geometries is crucial for high-speed and low-power DDR2 and DDR3 SDRAM in an increasingly mobile world. With the validation and customer qualification of the first component, a 512Mb DDR SDRAM, Infineon and Nanya are the industry?s second DRAM manufacturers to introduce the 90nm technology node. The extension of the portfolio with a 512Mb DDR2 SDRAM is expected in the second half of 2005. A variety of other products including 256Mb DDR2 and 1G DDR2 are to follow later on.

Process structures of 90nm further reduce chip size compared to the previous 110nm technology thereby increasing potential chip output per wafer by more than 30 percent. The expected productivity increase by shrinking the chip size combined with the use of 300mm wafers is the basis for a significant reduction of production cost per chip. The strategic development alliance of Infineon and Nanya also covers the next technology node with 70nm structures.

Except for its cost advantage, transition to smaller process geometries is crucial for high-speed and low-power DDR2 and DDR3 SDRAM in an increasingly mobile world. With the validation and customer qualification of the first component, a 512Mb DDR SDRAM, Infineon and Nanya are the industry?s second DRAM manufacturers to introduce the 90nm technology node. The extension of the portfolio with a 512Mb DDR2 SDRAM is expected in the second half of 2005. A variety of other products including 256Mb DDR2 and 1G DDR2 are to follow later on.