Nvidia Unveils Parker, The Latest SOC For Autonomous Vehicles

NVIDIA today took the cloak off Parker, the company's newest mobile processor that will power the autonomous vehicles in the future. Speaking at the Hot Chips conference in Cupertino, California, Nvidia revealed the architecture and underlying technology of this advanced processor, which is suited for automotive applications like self-driving cars and digital cockpits.

Nvidia mentioned Parker at CES earlier this year, when the company introduced the NVIDIA DRIVE PX 2 platform. That platform uses two Parker processors and two Pascal architecture-based GPUs to power deep learning applications. Nvidia claims that more than 80 carmakers, tier 1 suppliers and university research centers around the world are now using the DRIVE PX 2 system to develop autonomous vehicles. This includes Volvo, which plans to road test DRIVE PX 2 systems in XC90 SUVs next year.

Parker delivers performance and energy efficiency, while supporting features important to the automotive market such as deep learning, hardware-level virtualization for tighter design integration, a hardware-based safety engine for reliable fault detection and error processing, and feature-rich IO ports for automotive integration.

Built around NVIDIA’s highest performing and most power-efficient Pascal GPU architecture and the next generation of NVIDIA’s Denver CPU architecture, Parker delivers up to 1.5 teraflops of performance for deep learning-based self-driving AI cockpit systems.

Built around NVIDIA’s highest performing and most power-efficient Pascal GPU architecture and the next generation of NVIDIA’s Denver CPU architecture, Parker delivers up to 1.5 teraflops of performance for deep learning-based self-driving AI cockpit systems.

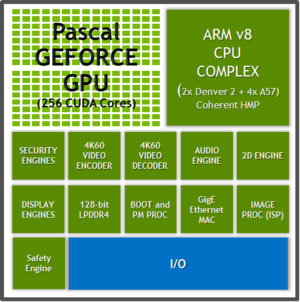

In addition, Parker delivers 50 to 100 percent higher multi-core CPU performance than other mobile processors, Nvid aclaims. This is thanks to its CPU architecture consisting of two next-generation 64-bit Denver CPU cores (Denver 2.0) paired with four 64-bit ARM Cortex A57 CPUs. These all work together in a fully coherent heterogeneous multi-processor configuration.

The Denver 2.0 CPU is a seven-way superscalar processor supporting the ARM v8 instruction set and implements an improved dynamic code optimization algorithm and additional low-power retention states for better energy efficiency. The two Denver cores and the Cortex A57 CPU complex are interconnected through a proprietary coherent interconnect fabric.

A new 256-core Pascal GPU in Parker delivers the performance needed to run advanced deep learning inference algorithms for self-driving capabilities. And it offers the raw graphics performance and features to power multiple high-resolution displays, such as cockpit instrument displays and in-vehicle infotainment panels.

Working in concert with Pascal-based supercomputers in the cloud, Parker-based self-driving cars can be continually updated with newer algorithms and information to improve self-driving accuracy and safety.

Parker includes hardware-enabled virtualization that supports up to eight virtual machines. Virtualization enables carmakers to use a single Parker-based DRIVE PX 2 system to concurrently host multiple systems, such as in-vehicle infotainment systems, digital instrument clusters and driver assistance systems.

Parker is also a scalable architecture. Automakers can use a single unit for efficient systems. Or they can integrate it into more complex designs, such as NVIDIA DRIVE PX 2, which employs two Parker chips along with two discrete Pascal GPU cores.

In fact, DRIVE PX 2 delivers 24 trillion deep learning operations per second to run the most complex deep learning-based inference algorithms. Such systems deliver the supercomputer level of performance that self-driving cars need to safely navigate through all kinds of driving environments.

To address the needs of the automotive market, Parker includes features such as a dual-CAN (controller area network) interface to connect to the numerous electronic control units in the modern car, and Gigabit Ethernet to transport audio and video streams. Compliance with ISO 26262 is achieved through a number of safety features implemented in hardware, such as a safety engine that includes a dedicated dual-lockstep processor for reliable fault detection and processing.

Parker is architected to support both decode and encode of video streams up to 4K resolution at 60 frames per second.

NVLink 2.0 Coming In Power9 servers next year

In related news, Nvidia's groundbreaking interconnect NVLink 2.0 is coming into IBM's upcoming Power9 chip, and servers using the chip will be available next year.

Nvidia hasn't yet announced when GPUs with NVLink 2.0 would come out, but they could be available around the same time as the new Power9 servers come out. IBM is projecting Power9 servers to be out by the middle of next year.

A presentation on Nvidia's website says NVLink 2.0 will be in GPUs code-named Volta, which also will come out next year.

Each NVLink 2.0 lane in the Power9 chip will communicate at 25Gbps (bits per second), seven to 10 times the speed of PCI-Express 3.0, according to IBM. Power9 will have multiple communication lanes for NVLink 2.0, and they could provide massive throughput when combined.

Recent Nvidia GPUs like the Tesla P100 are based on the company's Pascal architecture and use NVLink 1.0. The Volta GPU architecture will succeed Pascal, also used in GPUs like the GeForce GTX 1080.

For now, the NVLink 2.0 I/O is designed for Nvidia GPUs, and no other component works with the interconnect.