Intel Demonstrates 32nm Chip and Nehalem Microprocessor Architecture

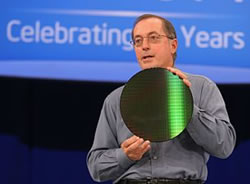

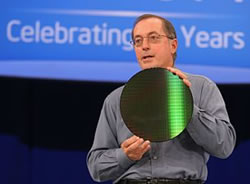

Intel President and CEO Paul Otellini on Thusday outlined new products, chip designs and manufacturing technologies at the Intel Developer Forum (IDF).

Speaking to industry leaders, developers and industry watchers, Otellini showed the industry's first working chips built using 32 nanometer (nm) technology. Intel's 32nm process technology is on track to begin production in 2009.

Otellini also described the near-term advantages computer users will experience with Intel's upcoming 45nm family of Penryn processors, which are based on its high-k metal gate transistor technology. The 45nm processors will be available from Intel in November. The company also demonstrated for the first time the next-generation chip architecture codenamed Nehalem, due out next year.

Penryn, along with the Silverthorne family of 45nm processors (available next year) will have the small feature size, low-power requirements and high-performance capabilities to meet a wide variety of computing needs from handheld Internet computers to high-end servers. Intel will quickly ramp the technology with plans to introduce 15 new 45nm processors by the end of the year and another 20 in the first quarter of 2008.

Penryn, along with the Silverthorne family of 45nm processors (available next year) will have the small feature size, low-power requirements and high-performance capabilities to meet a wide variety of computing needs from handheld Internet computers to high-end servers. Intel will quickly ramp the technology with plans to introduce 15 new 45nm processors by the end of the year and another 20 in the first quarter of 2008.

"We expect our Penryn processors to provide up to a 20 percent performance increase while improving energy efficiency," said Otellini. "Intel's breakthrough 45nm silicon process technology allows us to provide low-cost, extremely low-power processors for innovative small form factor devices while delivering high-performance, multi-core, multi-featured processors used in the most advanced systems."

Otellini also announced that Intel's 45nm processors and 65nm chipsets would use halogen-free packaging technology beginning in 2008.

Looking to 2008, Otellini made the first public demonstration of Intel's Nehalem processor and said the company is on track to deliver the new processor design in the second half of the year. The Nehalem architecture will be the first Intel processor to use the QuickPath Interconnect system architecture. Quickpath will include integrated memory controller technology and improved communication links between system components to significantly improve overall system performance.

"Nehalem is an entirely new architecture that leverages Intel's Core Microarchitecture, bringing leading-edge performance advantages, power efficiency and important new server features to market just a year after Intel leads the industry to 45nm technology," said Otellini.

Otellini also showed the world's first 300mm wafer built using next-generation 32nm process technology. The company plans to introduce processors built on 32nm technology in 2009.

Intel's 32nm test chips incorporate logic and memory (static random access memory --SRAM) to house more than 1.9 billion transistors. The 32nm process uses the company's second-generation high-k and metal gate transistor technology.

This additional performance made possible by Intel's push to drive chip design and manufacturing technology forward will not only be seen in computing, but will enable more realistic graphics capabilities. As a result, the company said it will be placing increased emphasis on using the power of its processors to enhance key technologies such as visual computing and graphics.

Otellini also announced that a version of a Penryn dual-core processor operating at 25 watts will be available on the upcoming Montevina platform, which will include Intel's mobile WiMAX silicon. Several equipment manufacturers are already planning to introduce Montevina-based notebook PCs starting next year when the platform is introduced. Overall, WiMAX is expected to reach more than 1 billion people worldwide by 2012.

At the same event, Intel Corporation executive Patrick Gelsinger announced the QuickAssist Technology, first disclosed at the IDF in Beijing in April. QuickAssist is Intel's suite of hardware and software technologies addressing the requirements of accelerators in enterprise platforms. He reviewed the first Intel device to include the Intel QuickAssist Integrated Accelerator for cryptography, codenamed Tolapai.

With availability targeted for 2008, Tolapai ? a system on a chip ? will deliver improvements in power-efficient performance and form factor with up to eight times the IP Security throughput, up to 20 percent reduction in power, and up to a 45 percent smaller footprint over previous multi-component security solutions in embedded and communications market segments.

On the heels of the latest-generation roll-out of Intel vPro processor technology, Gelsinger revealed plans to further evolve security and PC management benefits through the 2008 product codenamed McCreary. McCreary will include new halogen and lead-free 45nm dual and quad-core processors, a new chipset codenamed Eaglelake, an integrated Trusted Platform Module (TPM) and a more secure, manageable data encryption solution codenamed Danbury.

On the heels of the latest-generation roll-out of Intel vPro processor technology, Gelsinger revealed plans to further evolve security and PC management benefits through the 2008 product codenamed McCreary. McCreary will include new halogen and lead-free 45nm dual and quad-core processors, a new chipset codenamed Eaglelake, an integrated Trusted Platform Module (TPM) and a more secure, manageable data encryption solution codenamed Danbury.

Danbury technology builds data encryption and decryption directly into the hardware providing greater protection of encryption keys and allows much simpler system management and key recovery. Intel Active Management technology also enables these operations to occur in "out-of-band" environments, meaning even if the OS is down or inoperable. Bob Heard, founder and chief executive officer of CREDANT Technologies, discussed how their software security solutions can be improved in the future by leveraging Danbury and vPro technology.

Gelsinger also pointed to a wall of computer systems that Intel will deliver to suit most users' computing and cost needs. He showed how customers, such as Paradigm, will use Intel Xeon-based workstations with a new 1600MHz front side bus and Intel software tools to solve scientific problems, such as oil and gas exploration. Mark Barrenechea, president and chief executive officer of Rackable Systems, discussed Rackable's ICE Cube Modular Data Center on Wheels, which has 1400 quad core Intel Xeon servers in a single 40-foot truck container.

Gelsinger also discussed the improvements that solid state disk technology can bring to enterprise server and storage technology for IA platforms. He announced that products delivering substantial improvements in read performance and power savings from Intel utilizing non-volatile memory technology will be available next year.

Gelsinger shared his vision for I/O consolidation on Ethernet and steps to get to a converged network that supports both Fibre Channel over Ethernet (FCoE) and local area networks. In support of this vision, he announced availability of Intel 82598 10 Gigabit Ethernet Controller now with full support for FCoE solution stack coming in 2008.

Otellini also described the near-term advantages computer users will experience with Intel's upcoming 45nm family of Penryn processors, which are based on its high-k metal gate transistor technology. The 45nm processors will be available from Intel in November. The company also demonstrated for the first time the next-generation chip architecture codenamed Nehalem, due out next year.

Penryn, along with the Silverthorne family of 45nm processors (available next year) will have the small feature size, low-power requirements and high-performance capabilities to meet a wide variety of computing needs from handheld Internet computers to high-end servers. Intel will quickly ramp the technology with plans to introduce 15 new 45nm processors by the end of the year and another 20 in the first quarter of 2008.

Penryn, along with the Silverthorne family of 45nm processors (available next year) will have the small feature size, low-power requirements and high-performance capabilities to meet a wide variety of computing needs from handheld Internet computers to high-end servers. Intel will quickly ramp the technology with plans to introduce 15 new 45nm processors by the end of the year and another 20 in the first quarter of 2008.

"We expect our Penryn processors to provide up to a 20 percent performance increase while improving energy efficiency," said Otellini. "Intel's breakthrough 45nm silicon process technology allows us to provide low-cost, extremely low-power processors for innovative small form factor devices while delivering high-performance, multi-core, multi-featured processors used in the most advanced systems."

Otellini also announced that Intel's 45nm processors and 65nm chipsets would use halogen-free packaging technology beginning in 2008.

Looking to 2008, Otellini made the first public demonstration of Intel's Nehalem processor and said the company is on track to deliver the new processor design in the second half of the year. The Nehalem architecture will be the first Intel processor to use the QuickPath Interconnect system architecture. Quickpath will include integrated memory controller technology and improved communication links between system components to significantly improve overall system performance.

"Nehalem is an entirely new architecture that leverages Intel's Core Microarchitecture, bringing leading-edge performance advantages, power efficiency and important new server features to market just a year after Intel leads the industry to 45nm technology," said Otellini.

Otellini also showed the world's first 300mm wafer built using next-generation 32nm process technology. The company plans to introduce processors built on 32nm technology in 2009.

Intel's 32nm test chips incorporate logic and memory (static random access memory --SRAM) to house more than 1.9 billion transistors. The 32nm process uses the company's second-generation high-k and metal gate transistor technology.

This additional performance made possible by Intel's push to drive chip design and manufacturing technology forward will not only be seen in computing, but will enable more realistic graphics capabilities. As a result, the company said it will be placing increased emphasis on using the power of its processors to enhance key technologies such as visual computing and graphics.

Otellini also announced that a version of a Penryn dual-core processor operating at 25 watts will be available on the upcoming Montevina platform, which will include Intel's mobile WiMAX silicon. Several equipment manufacturers are already planning to introduce Montevina-based notebook PCs starting next year when the platform is introduced. Overall, WiMAX is expected to reach more than 1 billion people worldwide by 2012.

At the same event, Intel Corporation executive Patrick Gelsinger announced the QuickAssist Technology, first disclosed at the IDF in Beijing in April. QuickAssist is Intel's suite of hardware and software technologies addressing the requirements of accelerators in enterprise platforms. He reviewed the first Intel device to include the Intel QuickAssist Integrated Accelerator for cryptography, codenamed Tolapai.

With availability targeted for 2008, Tolapai ? a system on a chip ? will deliver improvements in power-efficient performance and form factor with up to eight times the IP Security throughput, up to 20 percent reduction in power, and up to a 45 percent smaller footprint over previous multi-component security solutions in embedded and communications market segments.

On the heels of the latest-generation roll-out of Intel vPro processor technology, Gelsinger revealed plans to further evolve security and PC management benefits through the 2008 product codenamed McCreary. McCreary will include new halogen and lead-free 45nm dual and quad-core processors, a new chipset codenamed Eaglelake, an integrated Trusted Platform Module (TPM) and a more secure, manageable data encryption solution codenamed Danbury.

On the heels of the latest-generation roll-out of Intel vPro processor technology, Gelsinger revealed plans to further evolve security and PC management benefits through the 2008 product codenamed McCreary. McCreary will include new halogen and lead-free 45nm dual and quad-core processors, a new chipset codenamed Eaglelake, an integrated Trusted Platform Module (TPM) and a more secure, manageable data encryption solution codenamed Danbury.

Danbury technology builds data encryption and decryption directly into the hardware providing greater protection of encryption keys and allows much simpler system management and key recovery. Intel Active Management technology also enables these operations to occur in "out-of-band" environments, meaning even if the OS is down or inoperable. Bob Heard, founder and chief executive officer of CREDANT Technologies, discussed how their software security solutions can be improved in the future by leveraging Danbury and vPro technology.

Gelsinger also pointed to a wall of computer systems that Intel will deliver to suit most users' computing and cost needs. He showed how customers, such as Paradigm, will use Intel Xeon-based workstations with a new 1600MHz front side bus and Intel software tools to solve scientific problems, such as oil and gas exploration. Mark Barrenechea, president and chief executive officer of Rackable Systems, discussed Rackable's ICE Cube Modular Data Center on Wheels, which has 1400 quad core Intel Xeon servers in a single 40-foot truck container.

Gelsinger also discussed the improvements that solid state disk technology can bring to enterprise server and storage technology for IA platforms. He announced that products delivering substantial improvements in read performance and power savings from Intel utilizing non-volatile memory technology will be available next year.

Gelsinger shared his vision for I/O consolidation on Ethernet and steps to get to a converged network that supports both Fibre Channel over Ethernet (FCoE) and local area networks. In support of this vision, he announced availability of Intel 82598 10 Gigabit Ethernet Controller now with full support for FCoE solution stack coming in 2008.