Imagination Technologies Seeks Academia's Attention With MIPSfpga Program

Imagination Technologies is letting universities study its MIPS RTL code and explore a real working MIPS CPU, through a full teaching package with an FPGA-ready deliverables under the name MIPSfpga. The company says that that teaching the MIPS computer architecture to students is much easier and less complex than the x86 or ARM's approach.

Invented at Stanford University, the MIPS architecture has always been open to the extent that the original design was published. Imagination defended its intellectual property, but those that want to make their own MIPS CPU have flourished for over a decade; for example, one can find several open source MIPS simulators in the wild written by respectable universities.

However, letting free and open access to a fully-validated, current generation MIPS CPU, with non-obfuscated RTL code, yields some risks of fraudulent use.

So users that sign up the company's new MIPSfpga program have to accept a license whereby they are not allowed to turn the code into silicon for commercialization.

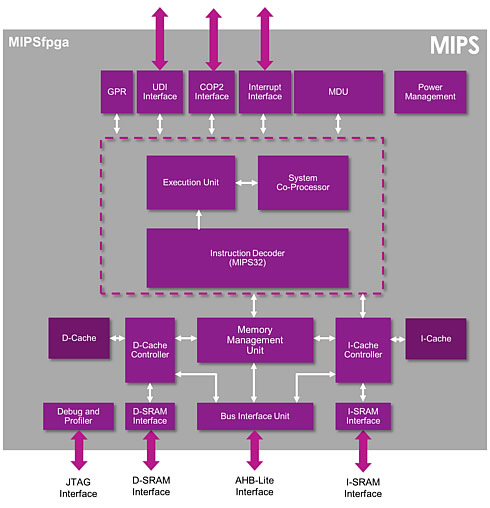

Through MIPSfpga, Imagination is providing universities with a simplified version of its popular MIPS microAptiv CPU core which has been configured by an academic specifically for academic use. The CPU has all the features (MMU, cache controllers, debug interfaces, etc.) required to run a full blown operating system (e.g. Linux).

It is offered as part of a complete free-to-download package for universities, together with a Getting Started Guide, teaching guide for professors, and examples designed to enable students to see how the CPU works and explore its capabilities.

Imagination Technologies will also offer technical support to ensure teachers start from a known good position rather than from MIPS-like or MIPS-compatible architectures.

With the materials, students can develop a CPU and take it through debug, running on an FPGA platform. This MIPS CPU configuration is designed to run on a low-cost FPGA platform, with guides available for the Digilent Nexys4 platform with a Xilinx Artix-7 FPGA, and the Terasic DE2 platform with an Altera Cyclone FPGA.

The MIPSfpga CPU and related materials are available for download from the Imagination University Programme website now for first phase users via an application process. Academics should visit http://community.imgtec.com/university to register for the IUP and learn more.

Phase two, starting in June, will require only a simple click-through agreement.

Imagination said that the very first people to get their hands on MIPSfpga will be the attendees at the first Workshops at Harvey Mudd College on May 13th and 14th.