Microsoft Joins Hybrid Memory Cube Consortium

Microsoft has joined the Hybrid Memory Cube Consortium

(HMCC), a consortium, led by Micron Technology and

Samsung Electronics.

The HMCC is a collaboration of original equipment

manufacturers (OEMs), enablers and integrators who are

cooperating to develop and implement an open interface

standard for a new memory technology called the Hybrid

Memory Cube (HMC). Micron and Samsung, the initial

developing members of the HMCC, are working with

Altera, IBM, Open-Silicon, Xilinx and now Microsoft to

accelerate widespread industry adoption of HMC

technology.

The technology will enable highly efficient memory solutions for applications ranging from industrial products to high-performance computing and large-scale networking. The HMCC's team of developers plans to deliver a draft interface specification to "adopters" that are joining the consortium. Then, the combined team of developers and adopters will refine the draft and release a final interface specification at the end of this year.

"HMC technology represents a major step forward in the direction of increasing memory bandwidth and performance, while decreasing the energy and latency needed for moving data between the memory arrays and the processor cores, " said KD Hallman, General Manager of Microsoft Strategic Software/Silicon Architectures. "Harvesting this solution for various future systems could lead to better and/or novel digital experiences."

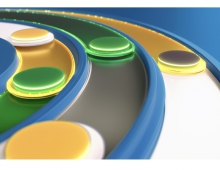

One of the primary challenges facing the industry is that the memory bandwidth required by high-performance computers and next-generation networking equipment has increased beyond what conventional memory architectures can provide. The term "memory wall" has been used to describe this dilemma. Breaking through the memory wall requires architecture such as the HMC that can provide increased density and bandwidth at significantly reduced power consumption.

Hybrid Memory Cube is a new DRAM memory architecture that combines high-speed logic process technology with a stack of through-silicon-via (TSV) bonded memory die. According to the consortium, it offers dramatic improvements in performance, breaking through the memory wall and enabling performance and bandwidth improvements - a single HMC can provide more than 15x the performance of a DDR3 module. The architecture of HMC is exponentially more efficient than current memory, utilizing 70% less energy per bit than DDR3 DRAM technologies. Hybrid Memory Cube's increased density per bit and reduced form factor contribute to lower total cost of ownership, by allowing more memory into each machine and using nearly 90% less space than today's RDIMMs.

The technology will enable highly efficient memory solutions for applications ranging from industrial products to high-performance computing and large-scale networking. The HMCC's team of developers plans to deliver a draft interface specification to "adopters" that are joining the consortium. Then, the combined team of developers and adopters will refine the draft and release a final interface specification at the end of this year.

"HMC technology represents a major step forward in the direction of increasing memory bandwidth and performance, while decreasing the energy and latency needed for moving data between the memory arrays and the processor cores, " said KD Hallman, General Manager of Microsoft Strategic Software/Silicon Architectures. "Harvesting this solution for various future systems could lead to better and/or novel digital experiences."

One of the primary challenges facing the industry is that the memory bandwidth required by high-performance computers and next-generation networking equipment has increased beyond what conventional memory architectures can provide. The term "memory wall" has been used to describe this dilemma. Breaking through the memory wall requires architecture such as the HMC that can provide increased density and bandwidth at significantly reduced power consumption.

Hybrid Memory Cube is a new DRAM memory architecture that combines high-speed logic process technology with a stack of through-silicon-via (TSV) bonded memory die. According to the consortium, it offers dramatic improvements in performance, breaking through the memory wall and enabling performance and bandwidth improvements - a single HMC can provide more than 15x the performance of a DDR3 module. The architecture of HMC is exponentially more efficient than current memory, utilizing 70% less energy per bit than DDR3 DRAM technologies. Hybrid Memory Cube's increased density per bit and reduced form factor contribute to lower total cost of ownership, by allowing more memory into each machine and using nearly 90% less space than today's RDIMMs.