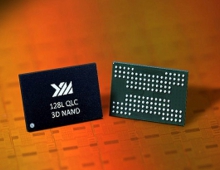

Western Digital Announces First 96-Layer 3D NAND Technology

Western Digital has successfully developed its next-generation 3D NAND technology, BiCS4, with 96 layers of vertical storage capability.

The company will start sampling the new memory to OEM customers in the second half of calendar year 2017 and initial production output is expected in calendar year 2018.

BiCS4, which was developed jointly with Western Digital's technology and manufacturing partner Toshiba, will be initially deployed in a 256-gigabit chip and will subsequently ship in a range of capacities, including a terabit on a single chip.

"Our successful development of the industry's first 96-layer 3D NAND technology demonstrates Western Digital's continued leadership in NAND flash and solid execution to our technology roadmap," said Dr. Siva Sivaram, executive vice president of memory technology at Western Digital. "BiCS4 will be available in 3-bits-per-cell and 4-bits-per-cell architectures, and it contains technology and manufacturing innovations to provide the highest 3D NAND storage capacity, performance and reliability at an attractive cost for our customers. Western Digital's 3D NAND portfolio is designed to address the full range of end markets spanning consumer, mobile, computing and data center."

The company also highlighted ongoing operations at its joint venture manufacturing facilities in Japan. In particular, the company reiterated its expectation that in calendar year 2017, the output mix of its 64-layer 3D NAND technology, BiCS3, will comprise more than 75 percent of its overall 3D NAND bit supply. The company now believes that, along with its partner Toshiba Corporation, the combined 64-layer 3D NAND bit output of the joint ventures in calendar year 2017 will be higher than any other industry supplier in calendar year 2017.