PCI Express 4.0 Specification Offers 16GT/s Performance, PCIe 5.0 Doubles it

PCI-SIG, the organization responsible for the widely adopted PCI Express (PCIe) industry-standard input/output (I/O) technology, today announced the release of the PCI Express 4.0, Revision 0.9 Specification, supporting 16GT/s data rates. The organization also announced 32GT/s as the next progression in speed for the PCIe 5.0 architecture.

speaking at the PCI-SIG Developers Conference 2017, Al Yanes, PCI-SIG Chairman and President, said that PCIe 4.0 specification is feature complete and going through final IP review.

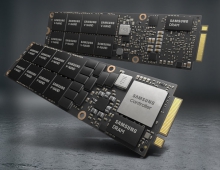

Originating as the cornerstone for I/O connectivity in personal computing, the PCIe architecture has become the interconnect of choice for the server and storage market. More recently, the PCIe architecture has also evolved into the backbone for the proliferating cloud ecosystem and served as the I/O attach point in mobile, IoT, networking and external I/O connectors.

The PCIe 4.0 architecture offers functional enhancements including extended tags and credits for service devices, reduced system latency, lane margining, superior RAS capabilities, scalability for added lanes and bandwidth, as well as improved I/O virtualization and platform integration.

PCI-SIG also today announced 32GT/s as the next progression in speed for the PCIe 5.0 architecture, targeting high-performance applications such as artificial intelligence, machine learning, gaming, visual computing, storage and networking. The architecture will use 128-/130-bit encoding to deliver up to 128 GBytes/s over 16 4-GB/s lanes. Slated for completion in 2019, the specification development is well underway with Revision 0.3 already available to PCI-SIG member companies.

For high-end networking like 400Gb Ethernet solutions and dual 200Gb/s InfiniBand, the PCIe 5.0 architecture operates at full duplex and provides up to 128GB/s in bandwidth. The higher bandwidth will serve accelerator and GPU attachments, as well as constricted form factor applications needing to increase channel width.

The 32G spec comes at a time when the rise of giant data centers has been driving serdes interconnects to rates up to 56 Gbits/second.

IBM is working on Power 9 that aims later this year to be the first commercial CPU to use PCIe Gen 4.