Intel Spotlights Research in Silicon Spin Qubits and Quantum Applications Development

During the American Physical Society (APS) March Meeting in Boston, researchers from Intel Labs will demonstrate the progress they are making toward developing a commercially viable quantum computing system.

The researchers will announce breakthroughs in hardware and software development for the quantum computing stack and the development of a tool that will speed the research and optimization of silicon spin qubit technologies.

Let's see the abstract of some of these papers that will presented at the meeting.

Mode Hybridization Analysis of Bus Resonators for a Superconducting Multi-Qubit Chip

Intel's researchers present an effective numerical method to analyze the mode hybridization in a superconducting multi-qubit chip. Surface code, an architecture for fault-tolerant quantum computing, requires qubits with connectivity to all nearest neighbors. This extensive interconnectivity together with a strong coupling coefficient among the qubits and resonators causes mode hybridization. A complete analysis of the chip is needed in these conditions to accurately predict the loaded frequency of the bus resonators and thereby also the gate time. The researchers present and experimentally verify a simulation method for analyzing the complete chip where finite-element electromagnetic simulation is combined with a numerical circuit simulation for accurate and fast computation.

Spin Qubits at Intel

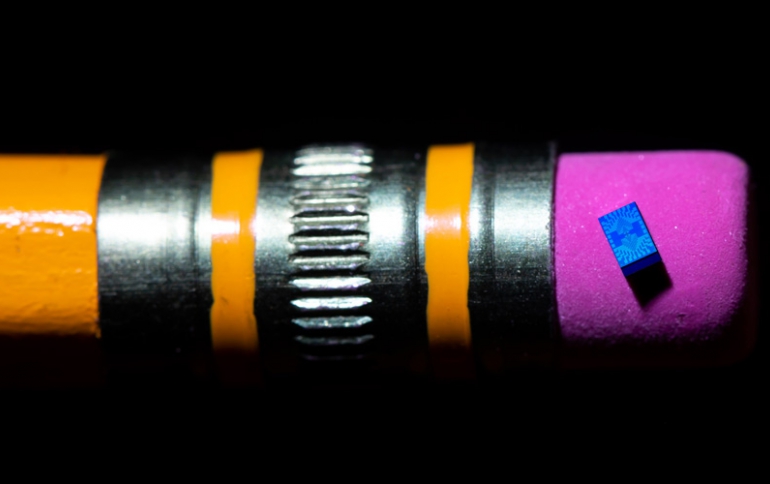

Intel is also developing a 300mm process line for spin qubit devices using immersion lithography and isotopically pure epitaxial silicon layers. Both Si-MOS and Si/SiGe devices are being evaluated in this multi-layer integration scheme. In this talk, researchers shared current progress toward spin qubits starting with substrate characterization. Transistors and quantum dot devices are then co-fabricated on the same wafer and allow calibration to Intel’s internal transistor processes. Electrical characterization and feedback is accomplished through wafer scale testing at both room temperature and 1.6K prior to milli-kelvin testing. Accelerated testing across a 300mm wafer provides a vast amount of data that can be used for continuous improvement in both performance and variability. This removes one of the bottlenecks toward a large-scale system: trying to deliver an exponentially fast compute technology with a slow and linear characterization scheme using only dilution refrigerators.

A Quantum Solution for Efficient Use of Symmetries in Exact Diagonalization of Many-Body Systems

The use of symmetries allows the block-diagonalization of the Hamiltonian of a many-body system, allowing it to be expressed in terms of symmetry-adapted basis states. The problem of finding the group representatives of these basis states and their corresponding symmetries is currently a memory/computational bottleneck on classical computers. The researchers apply Grover’s search in the form of a minimization procedure to solve this problem, improving upon the existing technique present in the literature to reduce the number of qubits and oracle calls. This quantum solution provides an exponential reduction in computational memory, and a quadratic speedup in time. The researchers discuss explicitly the full circuit implementation of Grover minimization as applied to this problem, finding that the oracle only scales as poly-log in the size of the search space. Further, the researchers design an error mitigation scheme that significantly reduces the effects of noise on the computation, showing how it can be run in the Noisy Intermediate Scale Quantum era.

Impact of Qubit Connectivity on Quantum Algorithm Performance

Quantum computing hardware is undergoing rapid development from proof-of-principle devices to scalable machines that could eventually challenge classical supercomputers on specific tasks. On platforms with local connectivity, the transition from one- to two-dimensional arrays of qubits is seen as a natural technological step to increase the density of computing power and to reduce the routing cost of limited connectivity. Here researchers map and schedule representative algorithmic workloads – the Quantum Fourier Transform (QFT) relevant to factoring, the Grover diffusion operator relevant to quantum search, and Jordan-Wigner parity rotations relevant to simulations of quantum chemistry and materials science – to qubit arrays with varying connectivity. In particular, the researchers investigate the impact of restricting the ideal all-to-all connectivity to a square grid, a ladder and a linear array of qubits. "Our schedule for the QFT on a ladder results in running time close to that of a system with all-to-all connectivity. Our results suggest that some common quantum algorithm primitives can be optimized to have execution times on systems with limited connectivities, such as a ladder and linear array, that are competitive with systems that have all-to-all connectivity," the researchers said.

Full 300mm Fin Based QD Device Characterization

Intel’s efforts toward the fabrication of spin qubit devices have required a comprehensive device characterization, from transistors and quantum dots, to qubits, which have been co-fabricated in the same die/wafer. In this talk, researchers present an in-depth device characterization, and the results from quantum dot devices manufactured in a full 300mm line. The researchers will give details of the fin based process flow, which yields high-charging energy devices (>35meV). The extraction of QD related figures of merit from room and low temperature testing (1.6K) are part of the method to rapidly screen 300mm wafers with thousands of devices that are used to determine the spin qubit devices that will be taken to the milli-kelvin measurements; keeping up with the pace of the 300mm fab output.

Intel Superconducting Qubits, Part 1: Performance Improvements towards Enabling Quantum Applications

Quantum processors based on superconducting materials with flux-tunable transmon qubits present many challenges, including minimizing flux and microwave xtalk, improving qubit frequency targeting, extending T1/T2 times, and ultimately maximizing gate fidelities. Here the researchers present their fabrication capabilities addressing some of these challenges with die sizes ranging from small laterally wire-bonded 2-qubit chips to larger flip-chip BGA-bonded 7-qubit and 17-qubit chips. Through improved die processing, including improvements to materials interfaces, integration of air bridges, and Josephson Junction fabrication improvements, they demonstrate low flux and microwave cross talk and qubit performance improvements resulting in 1Q and 2Q gate fidelities that enable algorithm exploration and execution.

Intel Superconducting Qubits, Part 2: Integration on Through-Silicon-Via (TSV) Substrates

Quantum computing holds the potential for significantly improving computing speed relative to classical computing for selected algorithms and applications. Many researchers using the transmon-style of circuit QED are producing chips with ever-increasing numbers of qubits. While higher numbers of qubits can increase the usefulness of algorithms that can be performed, the increase in chip size correspondingly shifts cavity and drum modes into a range where the qubits could be adversely affected. One solution is to implement through-silicon-vias (TSVs) and chip/cavity fuzz buttons to supply more ground connections. The researchers present recent microwave modeling and fabrication results on “flip-chips” containing TSVs for grounding and a ball-grid array die-package interface for electrical signals.