Intel Starts Sampling Stratix 10 FPGA For Smart and Connected Devices, Aero board And robotics kit Also Released

Intel has started sampling the Stratix 10 field programmable arrays, the industry’s first 14nm FPGA. Altera’s Stratix 10 has been manufactured on Intel’s 14nm tri-gate process technology with a new architecture called HyperFlex to meet the performance demands of high-end compute and data-intensive applications ranging from data centers, network infrastructure, cloud computing, and radar and imaging systems. It is also the first chip to use its embedded multi-die interconnect packaging technology.

FPGAs are a critical part of Intel’s growth strategy, which is being fueled by the virtuous cycle of growth. When speaking about Stratix 10 at IDF16, Intel CEO Brian Krzanich stated, "This thing is a beast," referring to the performance and density of Stratix 10.

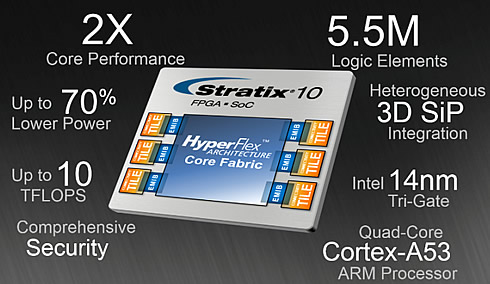

The capabilities of Stratix 10 include:

- 2X the core performance and over 5X the density compared to the previous generation.

- Up to 70 percent lower power than Stratix V FPGAs for equivalent performance.

- Up to 10 TFLOPS of single-precision floating point DSP performance.

- Up to 1 TBps memory bandwidth with integrated High-Bandwidth Memory (HBM2) in-package.

- Embedded quad-core 64-bit ARM Cortex-A53 processor

Within the data center, FPGAs are used to accelerate the performance of large-scale data systems. Stratix 10 FPGAs provide flexibility and performance-per-watt acceleration to address the data center needs.

Stratix 10 FPGAs can be used as a high-performance, multifunction accelerator in the data center, or be reconfigured in milliseconds to accelerate individual tasks.

About the HyperFlex technology

The key features of the HyperFlex technology are :

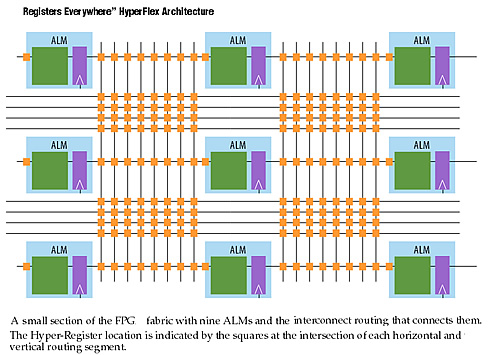

- Registers Everywhere

The "registers everywhere" in the interconnect routing, called Hyper-Registers, are distinct from the conventional registers that are contained within the adaptive logic modules (ALMs). A Hyper-Register is associated with each individual routing segment in the device; Hyper-Registers are also available at the inputs of all functional blocks such as ALMs, embedded memory (M20K) blocks, and digital signal processing (DSP) blocks. The Hyper-Registers are bypassable, allowing the design tools to select the optimal register location automatically, after place-and-route, to maximize core performance. Having Hyper-Registers throughout the interconnect means that performance tuning does not require additional ALM resources (unlike conventional architectures) and does not require additional changes or added complexity to the design’s place-and-route. Additionally, having hyper-Registers built into the interconnect helps to reduce routing congestion.

- Enhanced Core Clocking

The programmable clock tree synthesis allows system designers to create localized clock trees, reducing skew and timing uncertainty to obtain maximum core clocking performance. This capability is a key feature that allows the HyperFlex architecture to reach 2X performance. In addition, the core clocking uses intelligent branch-enables to reduce the dynamic power dissipation in

the clock networks.

- Hyper-Aware Design Flow

The Hyper-Aware design flow includes three new improvements:

- A Fast Forward Compile tool that allows performance exploration and guides the user to maximum design performance.

- A Hyper-Retimer step that supports performance optimization after place-and-route.

- Enhanced synthesis and place-and-route algorithms that use the Hyper-Register

Aero board And robotics kit released

Intel is also shipping its Aero Compute Board so you can get your drone in the sky.

The Aero Compute Board is priced at $399 and available on Intel's website. It's a complete drone board system in one unit, but you have to buy certain hardware, like rotor blades, separately.

The Aero Compute Board has LTE, 802.11ac Wi-Fi and a flight controller. The board uses Airmap SDKs for low-altitude flight management of drones. It has a quad-core Atom X7-Z8700 CPU code-named Cherry Trail, which is also used in the Surface 3. It has 4GB of LPDDR3 RAM, 16GB of flash storage, a micro-SD slot, a micro-HDMI port, and a wide set of connectors for adapters and breakout boards. The board features an Altera Max 10 FPGA, which can reprogrammed to deal with multiple input and output mechanisms. It will be compatible with Linux.

Intel has also started selling its new Robotics Development Kit for $249. The board is meant to be the guts of a robot, providing direction, navigation, decision-making and other capabilities. You can build robots at home with this developer kit.

Intel's Robotics Development Kit has an Atom x5-Z8350 chip and integrated graphics. It has 32GB of storage, 4GB of RAM, an HDMI port, a gigabit ethernet slot, four USB 2.0 ports and one USB 3.0 port. It has an Altera Max V FPGA to interface with external devices. The board will be compatible with Ubuntu 14.04 or 16.04.