Rambus Advances Differential Memory Signaling to 20Gpbs and Single-ended Memory Signaling to 12.8Gbps

Rambus has advanced differential signaling for SoC-to-memory interfaces to a 20 gigabits per second (Gbps) and developed innovations which can extend single-ended memory signaling to an unparalleled 12.8Gbps.

Rambus has also developed innovations which enable a seamless transition for memory architectures from single-ended to differential signaling as data rates rise to meet the performance requirements of future-generation graphics and gaming systems. Rambus will demonstrate its breakthroughs in memory signaling technology this week at DesignCon 2011.

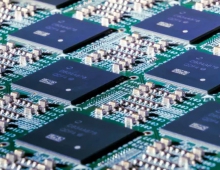

The latest technology advancements of Rambus Terabyte Bandwidth Initiative enable high power efficiency and compatibility to single-ended memory architectures, including GDDR5 and DDR3. With the addition of FlexMode interface technology, a multi-modal, SoC memory interface PHY, supporting both differential and single-ended signaling, can be implemented in a single SoC package design with no additional pins. Rambus has achieved a power efficiency of 6 milliwatts (mW) per Gbps when operating at 20Gbps in a 40nm-process silicon test vehicle.

Graphics cards and game consoles are the marquee performance products for consumers. The demand for photorealistic game play, 3D images, and a richer end-user experience is constantly pushing system and memory requirements higher. Todays high-end graphics processors support as much as 128 gigabytes per second (GB/s) of memory bandwidth, and future generations will push memory bandwidth to upwards of one terabyte per second (TB/s).

Through the Terabyte Bandwidth Initiative, Rambus has made key advancements using itssignaling and memory architecture expertise. These Rambus patented innovations include Fully Differential Memory Architecture (FDMA), FlexLink C/A and 32X data rate. The latest addition to these innovations, FlexMode interface technology, enables support of both differential and single-ended memory interfaces in a single SoC package design. FlexMode technology achieves this with no additional pins through programmable assignment of signaling I/Os to either data or command/address.

The latest technology advancements of Rambus Terabyte Bandwidth Initiative enable high power efficiency and compatibility to single-ended memory architectures, including GDDR5 and DDR3. With the addition of FlexMode interface technology, a multi-modal, SoC memory interface PHY, supporting both differential and single-ended signaling, can be implemented in a single SoC package design with no additional pins. Rambus has achieved a power efficiency of 6 milliwatts (mW) per Gbps when operating at 20Gbps in a 40nm-process silicon test vehicle.

Graphics cards and game consoles are the marquee performance products for consumers. The demand for photorealistic game play, 3D images, and a richer end-user experience is constantly pushing system and memory requirements higher. Todays high-end graphics processors support as much as 128 gigabytes per second (GB/s) of memory bandwidth, and future generations will push memory bandwidth to upwards of one terabyte per second (TB/s).

Through the Terabyte Bandwidth Initiative, Rambus has made key advancements using itssignaling and memory architecture expertise. These Rambus patented innovations include Fully Differential Memory Architecture (FDMA), FlexLink C/A and 32X data rate. The latest addition to these innovations, FlexMode interface technology, enables support of both differential and single-ended memory interfaces in a single SoC package design. FlexMode technology achieves this with no additional pins through programmable assignment of signaling I/Os to either data or command/address.