Renesas Develops the Basic Structure for Embedded DRAM with High Compatibility with Standard CMOS Logic Circuits

Renesas Electronics today announced the development of a basic structure for embedded DRAM (eDRAM) highly compatible with standard logic circuit design assets of the next generation system LSIs at the 28-nanometer (nm) node and beyond.

Due to the increasingly widespread use of digital TVs, digital still cameras and game consoles that produce high image quality, there is a growing demand for a technology that realizes higher-speed processing capability and low power consumption for consumer electronic devices and high-performance servers and networking devices. To address these needs, Renesas Electronics has been providing eDRAM products that achieve both high-speed processing and low power consumption and has shipped more than 200,000,000 units.

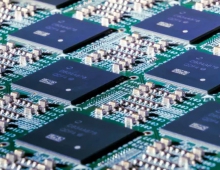

To assure both stable memory operation and sufficient data retention times, the capacitors used for the DRAM are formed after transistors have been formed on a silicon substrate, and finally the interconnects that connect these devices are formed on top of the eDRAM structure. As a result, in the logic circuit areas where no DRAM capacitors are formed, it is necessary to connect the transistors and interconnects through long "bypass contacts" that have the same height as the capacitors. However, as miniaturization progresses, it becomes necessary to reduce the diameter of and spacing between those bypass contacts. This makes it impossible to ignore the influence of the increasing resistance and parasitic capacitance of the bypass contacts and, unlike previous generations, it is difficult to reuse the IP developed for use in standard CMOS logic circuit without the bypass contacts.

Renesas Electronics has developed a new structure that embeds the DRAM capacitors and interconnects in the same layer by using improvements to the dielectric material and other aspects as a means for overcoming technological issues, and thereby has achieved significantly improved compatibility with ordinary system LSI manufacturing processes.

This new technology embeds the capacitors, which are the data storage elements in DRAM, in the interconnect layer used for the logic circuits. As a result, it will be possible to create embedded memory that seamlessly combines the globally standardized logic circuit IP with Renesas Electronics' eDRAM technology. Adoption of this new technology will also lead to more efficient and lower cost development of leading-edge devices to be fabricated at the 28-nm node and beyond.

To assure both stable memory operation and sufficient data retention times, the capacitors used for the DRAM are formed after transistors have been formed on a silicon substrate, and finally the interconnects that connect these devices are formed on top of the eDRAM structure. As a result, in the logic circuit areas where no DRAM capacitors are formed, it is necessary to connect the transistors and interconnects through long "bypass contacts" that have the same height as the capacitors. However, as miniaturization progresses, it becomes necessary to reduce the diameter of and spacing between those bypass contacts. This makes it impossible to ignore the influence of the increasing resistance and parasitic capacitance of the bypass contacts and, unlike previous generations, it is difficult to reuse the IP developed for use in standard CMOS logic circuit without the bypass contacts.

Renesas Electronics has developed a new structure that embeds the DRAM capacitors and interconnects in the same layer by using improvements to the dielectric material and other aspects as a means for overcoming technological issues, and thereby has achieved significantly improved compatibility with ordinary system LSI manufacturing processes.

This new technology embeds the capacitors, which are the data storage elements in DRAM, in the interconnect layer used for the logic circuits. As a result, it will be possible to create embedded memory that seamlessly combines the globally standardized logic circuit IP with Renesas Electronics' eDRAM technology. Adoption of this new technology will also lead to more efficient and lower cost development of leading-edge devices to be fabricated at the 28-nm node and beyond.