Imagination Takes On ARM With First MIPS CPU Core

Imagination Technologies will release its first MIPS Series5 'Warrior P-class' CPU core to device makers by the end of the year, as it aims at making the MIPS architecture a potential rival to ARM and x86.

MIPS chips are widely used in network gear such as routers and gateways, and in home media products including TVs and set-top boxes.

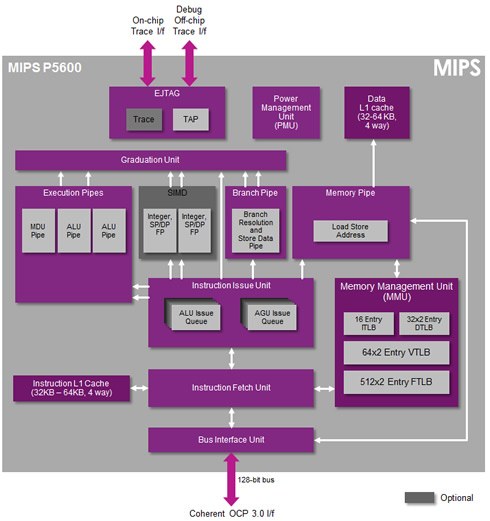

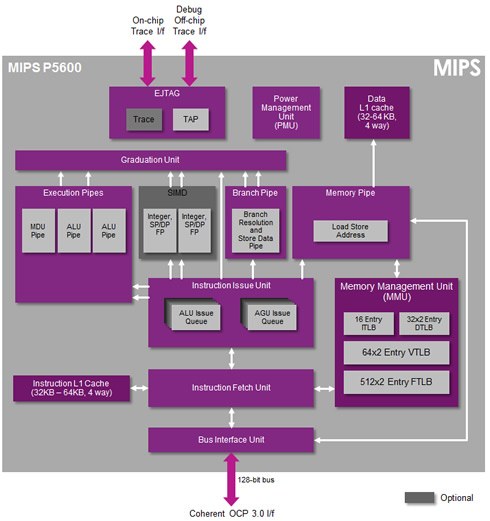

The new MIPS P5600 core delivers 32-bit performance together with low power characteristics in a silicon footprint up to 30% smaller than comparable CPU cores, meaning it could find its way in mobile, consumer and embedded applications.

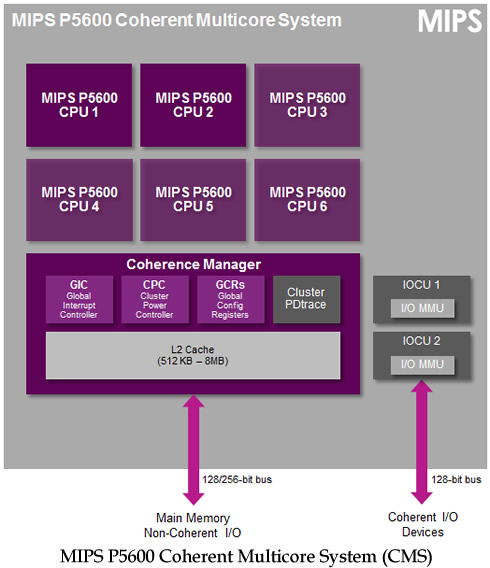

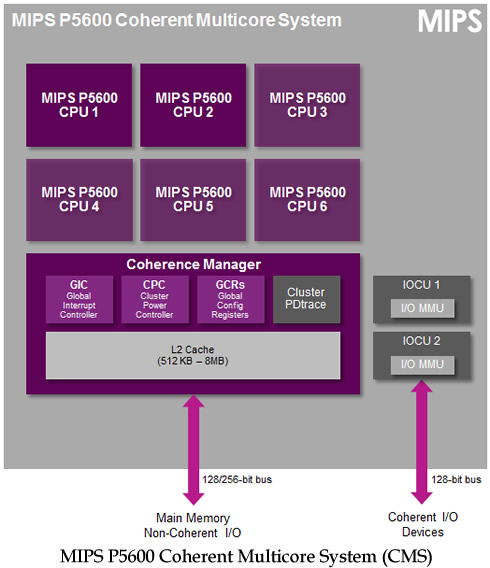

The MIPS P5600 supports full 128-bit SIMD designed for high performance on data parallel operations (DSP, codecs, image processing, DSP, low-level simple 2D graphics and other). It supports hardware virtualization (as defined in the MIPS r5 architecture announced December 2012), security features (secure content delivery, secure payments, identity protection e.t.c) and up to six cores per cluster with high-performance cache coherency.

In addition, Enhanced Virtual Addressing (EVA) enables more flexible usage of virtual address space, allowing for efficient use of memory for larger footprint Linux implementations. Extended Physical Addressing (XPA) also allows a 32-bit system to access physical memory beyond the 32-bit limit, up to 1 Terabyte (40-bits).

The MIPS SIMD architecture adheres to RISC philosophy, starting with thirty-two 128-bit architectural registers. Instructions were defined to be easily supported within high-level languages such as C or OpenCL for fast development of new code, as well as leverage of existing code.

The MIPS SIMD architecture adheres to RISC philosophy, starting with thirty-two 128-bit architectural registers. Instructions were defined to be easily supported within high-level languages such as C or OpenCL for fast development of new code, as well as leverage of existing code.

MIPS Series5 cores share a common datapath for execution of all 32-bit and 64-bit code, ensuring that 32-bit binaries for any 'Warrior' CPU will run without change on any 64-bit 'Warrior' CPU. MIPS Series5 64-bit CPUs do not need any separate datapaths to run legacy 32-bit applications, eliminating wasted silicon area and power when migrating to 64-bit.

With the P5600, Imagination has also implemented a range of performance enhancing features compared to earlier generations of MIPS cores, including widened datapaths and buses, increased L2 cache prefetching, enhanced load/store bonding, and optimizations for JIT and browser applications.

Imagination plans to release more MIPS 'Warrior' CPUs over the next 12 months to comprise a portfolio of 64-bit and 32-bit variants.

Tony King-Smith, EVP marketing, Imagination, says: "We are proud to announce this first MIPS 'Warrior P-class' CPU. This is about much more than the arrival of yet another CPU IP core. This is the start of something much bigger - the rollout of a comprehensive family of next-generation CPUs that will change the CPU IP landscape forever. As we continue to roll out MIPS Series5 products to address the applications spectrum from entry-level to the high-end, we will provide levels of performance, efficiency and functionality that surpass other offerings in the market. Many more Warriors are coming!"

According to Imagination, the MIPS P5600 achieves performance exceeding 5 CoreMark/MHz with 3.5 DMIPS/MHz. Compared to the ARM-based chips, it provides 1.2x - 2x performance gains on a wide variety of system-oriented benchmarks, including SPECint2000, Linpack, and Javascript/Browser tests, and 2x - 3x higher data movement on widely-used routines such as MemCopy libraries. It has also a 30% smaller silicon footprintthan the Samsung Exynos 5 Octa IP cores.

The P5600 will be available for licensing this quarter.

The new MIPS P5600 core delivers 32-bit performance together with low power characteristics in a silicon footprint up to 30% smaller than comparable CPU cores, meaning it could find its way in mobile, consumer and embedded applications.

The MIPS P5600 supports full 128-bit SIMD designed for high performance on data parallel operations (DSP, codecs, image processing, DSP, low-level simple 2D graphics and other). It supports hardware virtualization (as defined in the MIPS r5 architecture announced December 2012), security features (secure content delivery, secure payments, identity protection e.t.c) and up to six cores per cluster with high-performance cache coherency.

In addition, Enhanced Virtual Addressing (EVA) enables more flexible usage of virtual address space, allowing for efficient use of memory for larger footprint Linux implementations. Extended Physical Addressing (XPA) also allows a 32-bit system to access physical memory beyond the 32-bit limit, up to 1 Terabyte (40-bits).

MIPS Series5 cores share a common datapath for execution of all 32-bit and 64-bit code, ensuring that 32-bit binaries for any 'Warrior' CPU will run without change on any 64-bit 'Warrior' CPU. MIPS Series5 64-bit CPUs do not need any separate datapaths to run legacy 32-bit applications, eliminating wasted silicon area and power when migrating to 64-bit.

With the P5600, Imagination has also implemented a range of performance enhancing features compared to earlier generations of MIPS cores, including widened datapaths and buses, increased L2 cache prefetching, enhanced load/store bonding, and optimizations for JIT and browser applications.

Imagination plans to release more MIPS 'Warrior' CPUs over the next 12 months to comprise a portfolio of 64-bit and 32-bit variants.

Tony King-Smith, EVP marketing, Imagination, says: "We are proud to announce this first MIPS 'Warrior P-class' CPU. This is about much more than the arrival of yet another CPU IP core. This is the start of something much bigger - the rollout of a comprehensive family of next-generation CPUs that will change the CPU IP landscape forever. As we continue to roll out MIPS Series5 products to address the applications spectrum from entry-level to the high-end, we will provide levels of performance, efficiency and functionality that surpass other offerings in the market. Many more Warriors are coming!"

According to Imagination, the MIPS P5600 achieves performance exceeding 5 CoreMark/MHz with 3.5 DMIPS/MHz. Compared to the ARM-based chips, it provides 1.2x - 2x performance gains on a wide variety of system-oriented benchmarks, including SPECint2000, Linpack, and Javascript/Browser tests, and 2x - 3x higher data movement on widely-used routines such as MemCopy libraries. It has also a 30% smaller silicon footprintthan the Samsung Exynos 5 Octa IP cores.

The P5600 will be available for licensing this quarter.