ARM Unveiled New On-chip Interconnect Technology

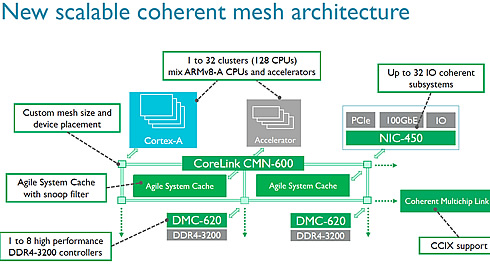

ARM has released new and faster on-chip interconnect technology. The CMN-600 ('coherent mesh network') is a direct update to CCN-500 series and promises to deliver scalability, performance and efficiency across multiple markets. The ARM CoreLink CMN-600 Coherent Mesh Network interconnect and CoreLink DMC-620 Dynamic Memory Controller enable the latest ARM-based SoCs to offer greater data throughput and "the lowest edge to cloud latency in the market," according to ARM.

"The demands of cloud-based business models require service providers to pack more efficient computational capability into their infrastructure," said Monika Biddulph, general manager, systems and software group, ARM. "Our new CoreLink system IP for SoCs, based on the ARMv8-A architecture, delivers the flexibility to seamlessly integrate heterogeneous computing and acceleration to achieve the best balance of compute density and workload optimization within fixed power and space constraints."

Optimized with the latest ARM Cortex-A processors, CoreLink CMN-600 and CoreLink DMC-620 are the only complete coherent backplane IP solution for the ARMv8-A architecture. Designers and system architects can scale high-performance SoC designs from 1 to 128 Cortex-A CPUs (32 clusters) with native ARM AMBA 5 CHI interfaces, the industry standard specification for high-performance on-chip communication.

Other key benefits and features include:

- New architecture achieving higher frequencies (2.5 GHz and higher), 50 percent lower latency 5x higher throughput and more than 1TB/s of sustained bandwidth

- New Agile System Cache with intelligent cache allocation to enhance any sharing of data between processors, accelerators and interfaces

- Supporting CCIX the open industry standard for coherent multi-chip processor and accelerator connectivity

- CoreLink DMC-620 includes integrated ARM TrustZone security and supports 1 to 8 channels of DDR4-3200 memory and 3D stacked DRAM for up to 1TB per channel.

According to ARM through simulations, the improved memory controller offers 50% lower latency and up to 5 times more bandwidth.

ARM claims that their simulations show that 64 A72s will run 2.5 times faster than 32 A72 cores, courtesy of the improved memory controller. Even more impressive is the claim that the maximum compute performance of a 64x A72 SoC can go up by a factor six compared to 16x A57 variant.

The question is who will use this interconnect technology in their server SoCs. Qualcomm or Avago/Broadcom are the most likely candidates.