GLOBALFOUNDRIES Partners with ASML for 28nm and 20nm Chip Tapeouts

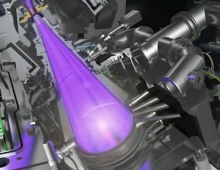

Brion Technologies, a division of ASML, on Monday announced a partnership with GLOBALFOUNDRIES to deliver high volume computational lithography capabilities for 28 nm and 20 nm tapeouts, while also accelerating the development of future nodes, including extreme ultraviolet (EUV) lithography.

The process window is very challenging for leading edge technologies and substantially impacts yield, time to market and ultimately profitability. ASML claims that its holistic lithography approach enables both process window enhancement and process window control from design to mask tapeout to chip manufacturing by leveraging the computational model accuracy that comes from tight integration with the ASML scanners including FlexRay & FlexWave.

GLOBALFOUNDRIES is working with Brion to ensure that their foundry customers have a cost effective semiconductor manufacturing capability available. Critical to achieving this is the use of Tachyon Flex, which is the platform architecture that allows the Tachyon applications to run on a customer's existing compute cluster, distributed across many thousands of CPU cores.

"At 28nm and below it is necessary to explore and realize every possible process window improvement to achieve a manufacturable patterning solution," said Chris Spence, Senior Fellow of GLOBALFOUNDRIES. "We have found that Brion's OPC and Computational Lithography solutions enable us to achieve this goal and ensure the best possible yield for GLOBALFOUNDRIES' customers."

In integrated circuits design, tape-out or tapeout is the final part of the design cycle before a photomask is manufactured. In its current practice (also known as 'mask data preparation' or MDP) chip makers perform checks and make modifications to the mask design specific to the manufacturing process. Optical proximity correction (OPC) is the most common example, which corrects for the diffraction and interference behavior of light when printing the sub-micron scale features of modern integrated circuit designs.

GLOBALFOUNDRIES is working with Brion to ensure that their foundry customers have a cost effective semiconductor manufacturing capability available. Critical to achieving this is the use of Tachyon Flex, which is the platform architecture that allows the Tachyon applications to run on a customer's existing compute cluster, distributed across many thousands of CPU cores.

"At 28nm and below it is necessary to explore and realize every possible process window improvement to achieve a manufacturable patterning solution," said Chris Spence, Senior Fellow of GLOBALFOUNDRIES. "We have found that Brion's OPC and Computational Lithography solutions enable us to achieve this goal and ensure the best possible yield for GLOBALFOUNDRIES' customers."

In integrated circuits design, tape-out or tapeout is the final part of the design cycle before a photomask is manufactured. In its current practice (also known as 'mask data preparation' or MDP) chip makers perform checks and make modifications to the mask design specific to the manufacturing process. Optical proximity correction (OPC) is the most common example, which corrects for the diffraction and interference behavior of light when printing the sub-micron scale features of modern integrated circuit designs.