Hynix Develops World's First 16GB DDR3 Single Package Chip

Hynix Semiconductor said Wednesday it has developed the world's largest dynamic random access memory (DRAM) for a single package, using the Through Silicon Via (TSV) technology.

The company succeded in stacking eight 2GB DDR3 (8-bit) DRAM chips in a single package, resulting to a 16GB DRAM chip.

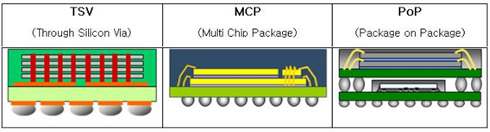

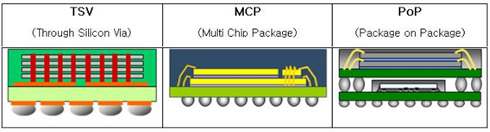

The existing MCP (Multi Chip Package) or PoP (Package On Package) chip stacking technologies are not sufficient enough to allow for stacking many DRAM chips, mainly due to wiring complexity and the increased size. TSVs are generally used to connect multiple ICs together in a package. In most packages, the stacked chips are wired together along their edges; this edge wiring slightly increases the length and width of the package and usually requires an extra "interposer" layer between the chips. In TSV packages, through-silicon vias replace edge wiring by creating vertical connections through the body of the chips. The resulting package has no added length or width and these layers are vertically connected layers behave as a single device.

By using TSV technology, ICs can pack a great deal of functionality into a small "footprint." In addition, critical electrical paths through the device can be drastically shortened, leading to faster operation.

Hynix said that TSV has advantages over previous technologies with a faster speed (50%) and lower power consumption (40%).

The new 16GB DDR3 DRAM chip can be used to meet demand for large-size memory in servers and other products, Hynix said. The company claims that large-size memory production technology using TSV will become a core part of the memory industry in two to three years.

On the other hand, TSV technology is the future memory chips, system semiconductors, image sensors (Image Sensor) and integrated into one package is expected to become a key technology.

Hynix expects to be able to start full-scale production of TSV 64GB DDR3 DRAM chips by 2013.

The existing MCP (Multi Chip Package) or PoP (Package On Package) chip stacking technologies are not sufficient enough to allow for stacking many DRAM chips, mainly due to wiring complexity and the increased size. TSVs are generally used to connect multiple ICs together in a package. In most packages, the stacked chips are wired together along their edges; this edge wiring slightly increases the length and width of the package and usually requires an extra "interposer" layer between the chips. In TSV packages, through-silicon vias replace edge wiring by creating vertical connections through the body of the chips. The resulting package has no added length or width and these layers are vertically connected layers behave as a single device.

By using TSV technology, ICs can pack a great deal of functionality into a small "footprint." In addition, critical electrical paths through the device can be drastically shortened, leading to faster operation.

Hynix said that TSV has advantages over previous technologies with a faster speed (50%) and lower power consumption (40%).

The new 16GB DDR3 DRAM chip can be used to meet demand for large-size memory in servers and other products, Hynix said. The company claims that large-size memory production technology using TSV will become a core part of the memory industry in two to three years.

On the other hand, TSV technology is the future memory chips, system semiconductors, image sensors (Image Sensor) and integrated into one package is expected to become a key technology.

Hynix expects to be able to start full-scale production of TSV 64GB DDR3 DRAM chips by 2013.