Intel Stratix 10 GX 10M FPGA Packs 10.2 Million Logic Elements

Intel introduced the Stratix 10 GX 10M, the world’s highest capacity FPGA, a large chiplet package with 43.3 billion transistors.

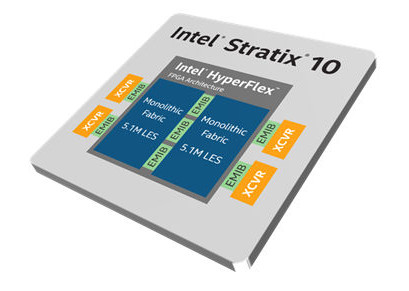

The Stratix 10 GX 10M has 10.2 million logic elements and uses EMIB to stitch two FPGA dies together along with four transceiver chiplets.

Being currently in production, this extremely dense FPGA is based on the existing Intel Stratix 10 FPGA architecture and Intel’s advanced Embedded Multi-die Interconnect Bridge (EMIB) technology. In the case of this new Intel Stratix 10 GX 10M FPGA, EMIB technology stitches two high-density Intel Stratix 10 GX FPGA core fabric die (with a capacity of 5.1 million LEs per die) along with appropriate I/O tiles. The EMIB data interface bus has 25,920 connections. Since each connection has a 2Gb/s throughput, this makes for an inter-die bandwidth of 6.5TB/s.

Intel says that the new Stratix 10 GX 10M FPGA with 10.2 million LEs is approximately 3.7x denser than the Intel Stratix 10 GX 1SG280 FPGA, previously the densest member of the Intel Stratix 10 device family.

The new FPGA is built on Intel’s 14nm process. Intel stated that the 10M contains 43.3 billion transistors. A rough estimate based on the provided package size yields a combined size of the two big dies of ~1400mm2 and a density of ~31MTr/mm2.

Xilinx’s 7nm Versal series currently tops out at 37 billion transistors. Nvidia's V100 has 21.2 billion transistors in 815mm2.

In August, Xilinx announced its 16nm Virtex UltraScale+ VU19P as the word’s highest-capacity FPGA. It was its third FPGA that used an interposer to connect four dies. The VU19P had 9 million logic elements and 35 billion transistors.

Intel claims the 10M delivers a 40% power reduction at equivalent capacity. Intel measured this by using four Stratix 10 2800s at the same capacity and frequency as the 10M.

One market in particular has a critical interest in always using the largest available FPGAs:

The ASIC prototyping and emulation market is typically interested in using the largest available FPGAs. There are several vendors offering commercial, off-the-shelf (COTS) ASIC prototyping and emulation systems participating in this market.

Many large semiconductor companies, including Intel, develop their own custom prototyping and emulation systems and use them to verify their largest, most complex, and therefore riskiest ASSP and SoC designs prior to tape out. ASIC emulation and prototyping systems can help design teams to lower this design risk by a significant amount. Consequently, Intel FPGAs including the Intel Stratix 10 FPGAs and even much earlier Stratix III, Stratix IV, and Stratix V devices have been used as the foundation in many of these emulation and prototyping systems for more than a decade.

Emulation and prototyping systems are designed to save semiconductor vendors millions of dollars by helping them identify and eradicate costly hardware and software design bugs before the chips are fabricated.

The 10.2 million LE Intel Stratix 10 GX 10M FPGA is already supported in the Intel Quartus Prime Software Suite with novel, specialized IP that explicitly supports ASIC emulation and prototyping.

The Stratix 10 GX 10M FPGA is the first Intel FPGA to use EMIB technology to logically and electrically bond two FPGA fabric die together to achieve the 10.2 million LE density. For this device, tens of thousands of connections link the two FPGA fabric die through multiple EMIB die, resulting in a high-bandwidth connection between the two monolithic FPGA fabric die.

Previously, Intel has used EMIB technology to connect I/O and memory tiles to FPGA die, which has resulted in the large and growing family of Intel Stratix 10 FPGAs. For example, Intel Stratix 10 MX devices incorporate either 8 or 16 Gbytes of EMIB-connected, 3D stacked HBM2 SRAM tiles. The recently announced Intel Stratix 10 DX FPGA incorporates EMIB-connected P tiles that provide PCIe 4.0 compatibility.

The P tile used in the Intel Stratix 10 DX FPGA is the first component-level device to appear on the PCI-SIG System Integrators List for PCIe 4.0. The same P tile is also tightly integrated into the recently announced Intel Agilex FPGA, giving that device PCIe 4.0 compatibility as well

These technologies allow Intel to build just about any sort of device imaginable by incorporating different semiconductor die – FPGAs, ASICs, eASIC structured ASICs, I/O tiles, 3D stacked memory tiles, photonic devices, etc. – into a System in Package (SiP) to meet specific customer needs.