New ARM Cortex A-72 Platform To Power 4K Graphics On Smartphones

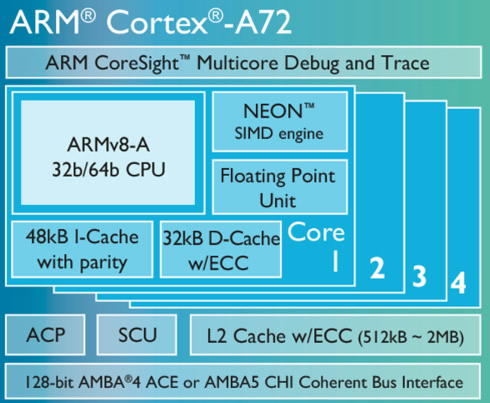

Chip designer ARM Holdings on Tuesday unveiled a new processor platform with improved computing performance and graphics aimed at smartphones and tablets to be launched next year. Available in 2016 mobile devices, ARM says that its new Cortex-A72 processor is the highest performing CPU technology available for developing mobile SoCs today. In target configurations, the Cortex-A72 processor promises to deliver CPU performance that is 50X greater than the leading smartphones from just five years ago.

The ARM IP suite also offers a significant graphics upgrade supporting stunning graphics at up to 4K120fps resolution. Devices with this new technology suite are expected to enter the market in 2016.

Alongside the Cortex-A72 processor is the new CoreLink CCI-500 interconnect and the new Mali-T880 GPU, ARM's highest performing and most energy-efficient mobile GPU, along with Mali-V550 video and Mali-DP550 display processors. To further ease chip implementation, the suite also includes ARM POP IP for the TSMC 16nm FinFET+ process.

"Our new premium mobile experience IP suite with the Cortex-A72 processor delivers a decisive step forward from the compelling user experiences provided by this year's Cortex-A57 based devices," said Pete Hutton, executive vice president and president, products groups, ARM. "For multiple generations, together with our partners, we have delivered the leading-edge of the premium mobile experience. Building on this, in 2016 the ARM ecosystem will deliver even slimmer, lighter, more immersive mobile devices that serve as your primary and only compute platform."

ARM's partners, including HiSilicon, MediaTek and Rockchip, have already licensed the Cortex-A72 processor, which is based on the ARMv8-A architecture that delivers 64-bit processing while providing backward compatibility to existing 32-bit software.

The Cortex-A72 processor will deliver sustained operation within the constrained mobile power envelope at frequencies of 2.5 GHz in a 16nm FinFET process and scalable to higher frequencies for deployment in larger form factor devices. It will offer 3.5X the performance of 2014 devices based on the Cortex-A15 processor and improved energy efficiency that delivers a 75 percent reduction in energy consumption when matching performance of 2014 devices. In addition, it can be combined with a Cortex-A53 CPU in ARM big.LITTLE processor configurations to deliver even

higher performance and efficiency.

The CoreLink CCI-500 Cache Coherent Interconnect enables big.LITTLE processing and delivers system power savings thanks to an integrated snoop filter. CoreLink CCI-500 delivers double the peak memory system bandwidth and offers a 30 percent increase in processor memory performance compared to the previous generation CoreLink CCI-400. This enables more responsive user interfaces and accelerates memory intensive workloads such as productivity applications, video editing and multi-tasking. CoreLink CCI-500 fully supports ARM TrustZone technology for a secure media path enabling protection of multimedia content when used with the Mali product family.

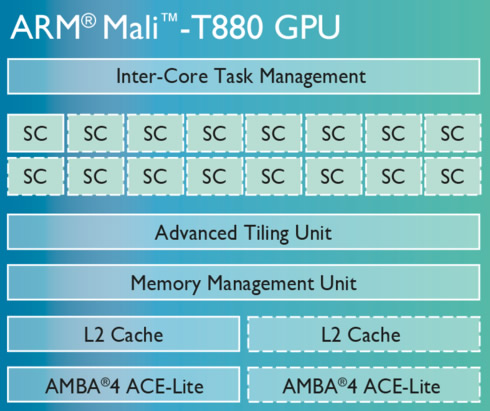

The new Mali-T880 GPU delivers 1.8X the graphics performance of today's Mali-T760 based devices and a 40 percent reduction in energy consumption across identical workloads. Native support for 10-bit YUV provides high fidelity for 4K content, complementing the Mali-V550 video processor and Mali-DP550 display processors.

In premium device configurations, the Mali-V550 video processor fully supports HEVC decode and encode on a single core. In addition, it offers scalability up to 4K120fps with its full eight cores. The Mali-DP550 display processor offers enhanced capabilities for offloading tasks such as composition, scaling, rotation and image post-processing from the GPU to maximize battery life.

The new POP IP for TSMC 16nm FinFET+ enables any silicon vendor to migrate from 32/28nm process nodes with predictable performance, power results and time-to-market. ARM POP IP will enable Cortex-A72 processors to sustain 2.5 GHz in smartphones and scale to higher frequencies for larger form-factor devices in typical conditions. POP IP also supports implementations of the Mali-T880 for TSMC 16nm FinFET+.

Over the course of 2015 and 2016, ARM expects significant adoption of Google Android 5.0 Lollipop in the premium mobile device market, further unleashing the capabilities of 64-bit ARMv8-A based CPUs.

ARM Mali-T880

| Features | Value | Description |

|---|---|---|

| Anti-Aliasing | 4x MSAA 8x MSAA 16x MSAA |

Hardware implemented Full Scene Multiple Sample Anti-Aliasing |

| API Support | OpenGL ES 1.1, 1.2, 2.0, 3.0, 3.1 OpenCL 1.1, 1.2 DirectX 11 FL11_2 RenderScript |

Full support for next-generation and legacy2D/3D graphics applications |

| Bus Interface | AMBA4 ACE-LITE |

Compatible with a wide range of bus interconnect and peripheral IP |

| L2 Cache | Configurable 256kB-2048kB | 256kB-512kB for every 4 shader cores |

| Memory System | Virtual Memory | Built-in Memory Management Unit (MMU) to support virtual memory |

| Multi-Core Scaling | 1 to 16 cores | Optimized for high energy efficiency to address the high-end mobile and consumer device requirements |

| Adaptive Scalable Texture Compression (ASTC) |

Low dynamic range (LDR) and high dynamic range (HDR). Supports both 2D and 3D images |

ASTC offers a number of advantages over existing texture compression schemes by improving image quality, reducing memory bandwidth and thus energy use. |

| ARM Frame Buffer Compression (AFBC) | 4x4 pixel block size | AFBC is a lossless image compression format that provides random access to pixel data to a 4x4 pixel block granularity. It is employed to reduce memory bandwidth both internally within the GPU and externally throughout the SoC |

| Transaction Elimination | 16x16 pixel block size | Transaction Elimination spots the identical pixel blocks between two consecutive render targets and performs a partial update to the frame buffer with the changed pixel blocks only, which reduces memory bandwidth and thus energy |

| Smart Composition | 16x16 pixel block size | Smart Composition extends the concept of Transaction Elimination to every stage of UI composition. Identical pixel blocks of input surfaces are not read, not processed for composition and not written to final frame buffer |

| Cortex-A72 Processor: Basic Information | |

|---|---|

| Architecture | ARMv8-A |

| Multicore | 1-4x SMP within a single processor cluster, and multiple coherent SMP processor clusters through AMBA 5 CHI or AMBA 4 ACE technology |

| ISA Support |

|

| Debug & Trace | CoreSight DK-A57 |