Samsung Develops 16-Chip Multi-Stack Package Technology

Samsung announced today that it has developed the industrys first process to enable production of a 16-chip multi-chip package (MCP) of memory.

Samsungs new 16-chip MCP technology, when applied to 8Gb NAND flash chips, can

enable up to a 16 gigabyte (GB) MCP solution.

Advanced multi-chip package technology requires a combination of key processes such as wafer thinning technology, redistribution layer technology, chip sawing technology and wire bonding technology.

To increase the number of chips stacked vertically, the need for further wafer thinning was a critical design obstacle. For the new 16-chip process, Samsung introduced wafer-thinning technology that eliminates 24 over 25 (24/25) of the thickness of each fabricated wafer to reduce the overall thickness to only 30-microns (um). This is just 65 percent the thickness of the 10-chip MCP wafer (45 um) Samsung developed in 2005 and similar to the size of a human cell, which measures 20 to 30 microns.

As part of its MCP technology, Samsung also developed a new laser-cutting technology to cut the wafer into individual chips. This new cutting process prevents the memory chips from breaking into pieces when they are cut using conventional blade sawing technology, which was originally designed only for sawing wafers up to 80 microns thick.

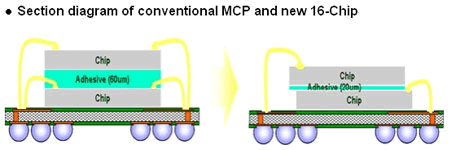

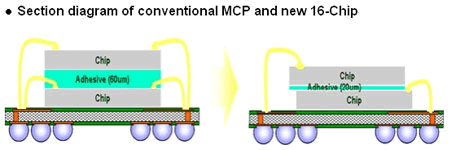

To vertically stack identically-sized dies (chips), a redistribution layer technology also is applied in Samsungs new multi-stack MCP process, to enable wafer fabricators to adhere the wire contacts from just one side, unlike the conventional method of extending wire connection from both sides of each chip. Along with a single wire contact per die, the dies are placed in a zigzag stack to minimize the use of space and the length of the wire connectors. Moreover, the thickness of the adhesive has been reduced to 20 microns bringing the height of a 16-die stack to 1.4mm. (A 10-chip MCP uses a 60-micron adhesive layer and has a total height of 1.6mm.)

Samsungs new 16-chip MCP was developed just one year after the development of the first 10-chip MCP. The new 16-chip MCP package technology provides the highest density solution yet developed for the creation of slimmer consumer electronics.

Advanced multi-chip package technology requires a combination of key processes such as wafer thinning technology, redistribution layer technology, chip sawing technology and wire bonding technology.

To increase the number of chips stacked vertically, the need for further wafer thinning was a critical design obstacle. For the new 16-chip process, Samsung introduced wafer-thinning technology that eliminates 24 over 25 (24/25) of the thickness of each fabricated wafer to reduce the overall thickness to only 30-microns (um). This is just 65 percent the thickness of the 10-chip MCP wafer (45 um) Samsung developed in 2005 and similar to the size of a human cell, which measures 20 to 30 microns.

As part of its MCP technology, Samsung also developed a new laser-cutting technology to cut the wafer into individual chips. This new cutting process prevents the memory chips from breaking into pieces when they are cut using conventional blade sawing technology, which was originally designed only for sawing wafers up to 80 microns thick.

To vertically stack identically-sized dies (chips), a redistribution layer technology also is applied in Samsungs new multi-stack MCP process, to enable wafer fabricators to adhere the wire contacts from just one side, unlike the conventional method of extending wire connection from both sides of each chip. Along with a single wire contact per die, the dies are placed in a zigzag stack to minimize the use of space and the length of the wire connectors. Moreover, the thickness of the adhesive has been reduced to 20 microns bringing the height of a 16-die stack to 1.4mm. (A 10-chip MCP uses a 60-micron adhesive layer and has a total height of 1.6mm.)

Samsungs new 16-chip MCP was developed just one year after the development of the first 10-chip MCP. The new 16-chip MCP package technology provides the highest density solution yet developed for the creation of slimmer consumer electronics.