Western Digital Announces Four-bits-per-cell Technology On 3D NAND

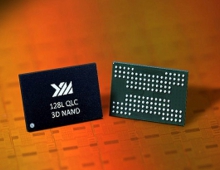

Western Digital has developed four bits per cell, X4, flash memory architecture offering on 64-layer 3D NAND, BiCS3, technology.

Building on the company's X4 for 2D NAND technology and past success in commercializing it, the company has now developed X4 for 3D NAND by leveraging its capabilities in silicon wafer processing and device engineering to provide sixteen distinct data levels in every storage node, and system expertise for overall flash management. BiCS3 X4 technology delivers storage capacity of 768 gigabits on a single chip, a 50 percent increase from the prior 512 gigabit chip that was enabled with the three bits per cell (X3) architecture. Western Digital will showcase removable products and solid-state drives built with BiCS3 X4 and systems capabilities in August at the Flash Memory Summit in Santa Clara, California.

The company expects to productize its 3D NAND X4 technology across multiple end-use applications that can take advantage of the higher capacity points supported by X4. Future generations of 3D NAND technology, including the 96-layer BiCS4, are also expected to feature X4 capabilities.