IBM Debuts DDR Alternative at Hot Chips

IBM presented at Hot Chips a new interface for the 2020 version of its Power 9 CPUs.

The Open Memory Interface (OMI) will enable packing on a server more main memory at higher bandwidth than DDR, and as a potential Jedec standard could rival GenZ and Intel’s CLX.

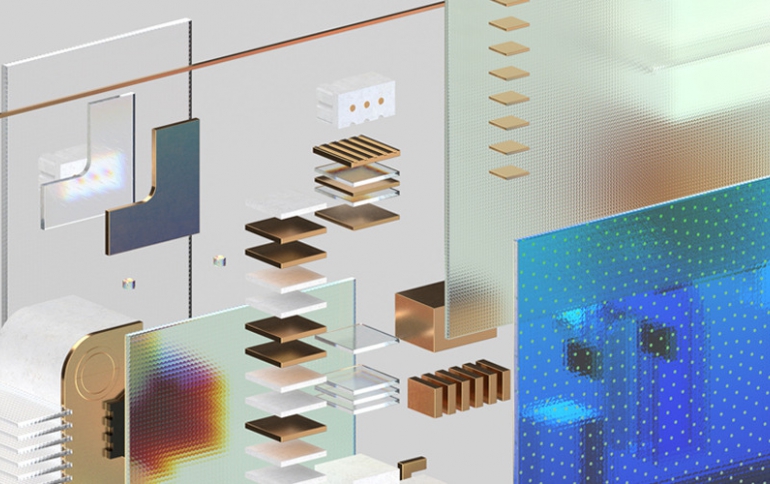

OMI removes the memory controller from the host, relying instead on a controller on a relatively small DIMM card. Microchip’s Microsemi division already has a DDR controller running on cards in IBM’s labs. The approach promises to deliver up to 4TBytes memory on a server at about 320GBytes/second or 512GB at up to 650GB/s sustained rates. Its cost is in the Microchip controller that adds at least 4-nanosceonds latency and dissipates about 4W, about half of which is mitigated by removing a DDR PHY from the host.

IBM envisions future controllers enabling OMI used with graphics DRAMs as an alternative to increasingly popular but expensive and HBM stacks. At about 80ns latency it could also be an attractive alternative to GenZ which can generate up to 400ns latency, said William Starke, an IBM processor architect.

OMI is based on 96 lanes of 25G serdes in IBM’s Power 9 Advanced I/O (AIO) chip. IBM optimized the serdes for lowest power and die size by limiting their frequency levels. The serdes offer up to 600GBytes/s of bandwidth that can be configured flexibly to serve OMI or the new generation of Nvidia’s NVLink GPU interconnect or IBM’s OpenCAPI 4.0 for other accelerators.

IBM’s next-generation Power 10 will move to 32-50G serdes to continue to enhance I/O and acceleration. Its roadmap shows Xilinx and partners will not get support from IBM for their CCIX cache-coherent interconnect that vies with Intel’s CLX.

The Power AIO is a 14nm chip that also supports 48 lanes of PCIe Gen4. The Power 10 in 2021 will be on a new process node with new core and transistor designs supporting PCIe Gen 5 and 800GB/s sustained memory bandwidth.