Sony's Pregius S Stacked CMOS Image Sensor Technology Delivers Both High Performance and Miniaturization

Sony has developed Pregius S, a stacked CMOS image sensor technology that employs Sony's proprietary global shutter function with back-illuminated pixel structure to deliver both high imaging performance and miniaturization.

The new sensor technology has been designed for industrial equipment used in fields such as manufacturing, inspection, and logistics that require higher precision and higher processing speeds.

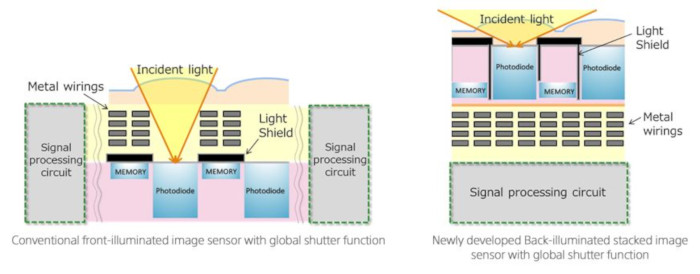

Conventional CMOS image sensors equipped with global shutter function temporarily store charge signals in the memory area located next to the photodiode to resolve image distortion (focal plane distortion) caused by the time shift due to the row-by-row readout. In front-illuminated CMOS image sensors, there is a wiring layer on the silicon substrate forming the photodiode, and with such a structure, the benefit is that it is easy to form a light shield for protecting the charge signal temporarily stored in the memory area from leaked light. For this reason, conventional CMOS image sensors with global shutter function have adopted a front-illuminated pixel structure. However, the wiring on top of the photodiode hinders the incident light, which creates an issue when attempting to miniaturize the pixels.

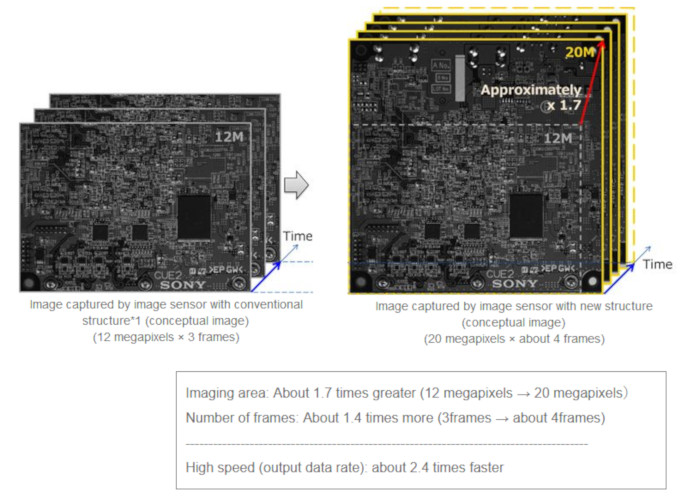

Sony has developed a proprietary pixel structure that achieves the global shutter function on a back-illuminated structure that has superior sensitivity characteristics, thereby resolving the issue of miniaturization. Normally, when pixels are miniaturized, the sensitivity and saturation characteristics deteriorate, but the new Sony technology enables a reduction in pixel size to 2.74 μm while maintaining performance of those characteristic, thereby achieving about 1.7 times higher resolution than conventional front-illuminated CMOS image sensors. This makes it possible to measure and inspect objects in a wider area and with higher accuracy in manufacturing, inspection, logistics and other applications. Moreover, thanks to the high degree of freedom of the wiring layout of back-illuminated pixel structures, a high speed of about 2.4 times that of conventional can be achieved, thereby contributing to significant productivity improvement, including shorter measurement and inspection process times.

In addition, the sensor’s stacked structure makes it possible to mount various signal processing circuits, whereby it is possible to realize smart functions such as signal processing only for the necessary part of the measurement and inspection images in a smaller size compared to conventional sensors. That, in turn, makes it possible to reduce the load of the subsequent processing and reduce the amount of data to be held on to, thereby contributing to the realization of highly efficient, energy-saving systems.

Sony will work to develop products equipped with this stacked CMOS image sensor employing its proprietary global shutter function with back-illuminated pixel structure for various industrial applications and intelligent transportation systems, including development of derivatives for signal processing circuits to be mounted.

Sony plans to start shipping sample units in the summer of 2019 or later.

Imaging performance

- Number of pixels: about 1.7 times more

- Quantum efficiency (Peak QE): +20%

- Saturation signal volume (per unit area): +44%

- Dynamic range: +12%

- Incident light angle dependence characteristic (sensitivity to light with an incident angle of 20°): about double

- High speed (output data rate): about 2.4 times