Synopsys and Cadence Design Platforms Certified by Samsung Foundry for 5LPE Process with EUV Technology

The Cadence digital full flow and the Synopsys Fusion Design Platform

have achieved certification for the Samsung Foundry 5nm Low-Power Early (5LPE) process with Extreme Ultraviolet (EUV) lithography technology.

The AI-enhanced, cloud-ready Fusion Design Platform provides full-flow quality-of-results (QoR) and time-to-results (TTR), enabling the full entitled performance and low power delivered by Samsung's 5LPE process technology to accelerate the next wave of semiconductor designs, including high-performance computing (HPC), automotive, 5G, and artificial intelligence (AI) market segments.

"Through our 7-nanometer product shipment and the successful completion of 5-nanometer process development, we've proven our capabilities in EUV-based nodes. Using the Synopsys Fusion Design Platform, our mutual customers will be able to design the most competitive 5LPE SoC products for the full entitled performance and low power applications," said JY Choi, vice president of Foundry Design Technology Team at Samsung Electronics. "Synopsys continues to be our vendor of choice for collaboration on new node development and enablement, so our foundry customers can confidently ramp their designs to volume production in all market segments, including automotive, AI, high-performance computing, and mobile."

Samsung Foundry certified the Fusion Design Platform using the 64-bit Arm Cortex-A53 and Cortex-A57 processors, which are based on the Armv8 architecture. Key tools and features of the Synopsys Fusion Design Platform optimized for Samsung 5LPE process technology include:

- Fusion Compiler RTL-to-GDSII Solution: Optimized full-flow support for latest 5LPE design rules delivering optimum design routability and convergence coupled to fastest TTR

- IC Compiler II place-and-route: EUV single-exposure-based routing with optimized 5LPE design rule support, single fin variant-aware legalization, and via stapling to ensure maximum utilization while minimizing dynamic power

- Design Compiler Graphical and Design Compiler NXT RTL synthesis: Correlation, congestion reduction, pin access-aware optimization, 5LPE design rule support, and physical guidance for IC Compiler II

- IC Validator physical signoff: Cloud-optimized physical signoff including DRC, LVS, and Fill. Innovative Explorer DRC and Live DRC technologies for enhanced productivity

- PrimeTime timing signoff: Near-threshold ultra-low voltage variation modeling, via variation modeling, and placement rule-aware engineering change order (ECO) guidance

- StarRC parasitic extraction: EUV single pattern-based routing support, and new extraction technologies, such as coverage-based via resistance and vertical gate resistance modeling

- RedHawk Fusion: ANSYS RedHawk-driven EM/IR analysis and optimization within place-and-route

- Synopsys TestMAX DFT and Synopsys TestMAX ATPG test: FinFET-based, cell-aware, and slack-based transition testing for higher test quality

- Formality equivalence checking: UPF-based equivalence checking with state transition verification

Seperately, the Cadence tools have been confirmed to meet Samsung Foundry’s technology requirements.

“As part of our longstanding collaboration with Cadence, we’ve confirmed that its digital full-flow meets and exceeds the requirements for designing with the 5LPE process technology,” said Jung Yun Choi, vice president of the Design Technology Team at Samsung Electronics. “By deploying the latest Cadence market-leading digital flow and Samsung advanced-node technology, customers can confidently create innovative designs for emerging high-end markets such as the mobile, networking, server, automotive, industrial, and artificial intelligence markets.”

The Cadence digital flow was certified by Samsung using the Arm Cortex-A53 and Cortex-A57 cores for the 5LPE process. To ensure the Cadence flow is easy to understand and use, it incorporates a Cadence flow manager with a common user interface across the complete toolset. The Cadence tools optimized for the Samsung 5LPE process include the Genus Synthesis Solution, Innovus Implementation System, Joules RTL Power Solution, Conformal Equivalence Checking, Conformal Low Power, Modus DFT Software Solution, Quantus Extraction Solution, Tempus Timing Signoff Solution, Voltus IC Power Integrity Solution, Physical Verification System, Litho Physical Analyzer and Cadence CMP Predictor.

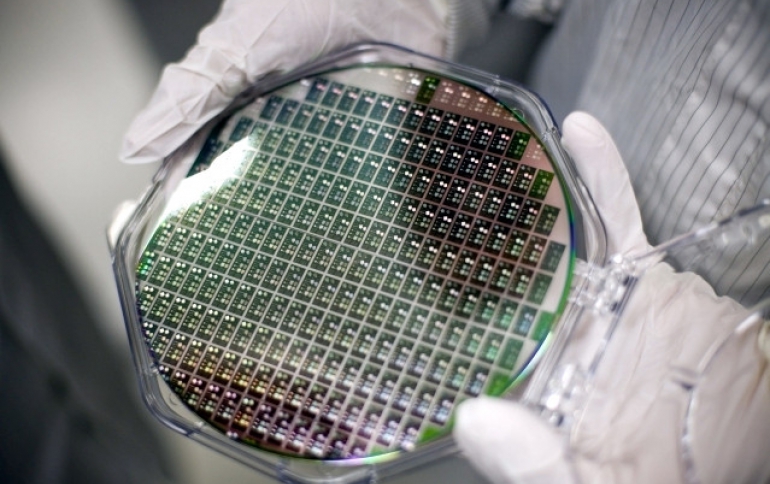

Samsung’s 5LPE technology relies on FinFET transistors with a new standard cell architecture and uses both DUV and EUV step-and-scan systems. The new fabrication process enables chip designers to reuse 7LPP IP on ICs designed for 5LPE while enjoying all benefits the latter provides. When compared to 7LPP, the new technology has an up to 25% higher ‘logic efficiency’, it also enables chip developers to reduce power consumption of their designs by 20% or improve their performance by 10%.

The set of tools from Candence and Synopsys that is certified by Samsung includes compilers, validators, power circuit optimizers as well as EUV-specific tools.

Since Samsung’s 5LPE uses more EUV layers than the company’s 7LPP process, expect it to be used on Samsung’s upcoming EUV fab in Hwaseong. The production line is set to cost 6 trillion Korean Won ($4.615 billion), it is expected to be completed in 2019, and start high volume manufacturing in 2020.