AMD Demonstrates 7nm "Rome" CPU Powered by "Zen 2" Processor Cores and Chiplet Design

AMD today detailed its upcoming 7nm compute product portfolio designed to extend the capabilities of the modern datacenter.

During the event, AMD shared new specifics on its upcoming "Zen 2" processor core architecture, detailed its chiplet-based x86 CPU design and provided the first public demonstration of its next-generation 7nm EPYC server processor codenamed "Rome".

AMD Compute Architecture Updates

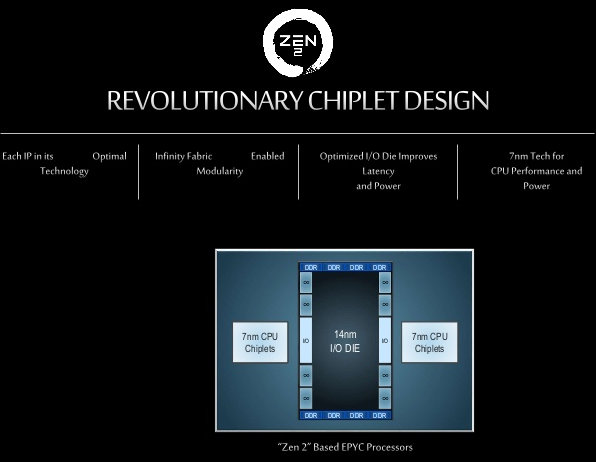

AMD for the first time detailed its upcoming "Zen 2" high-performance x86 CPU processor core that is the result of a modular design methodology. This modular system design uses an enhanced version of AMD Infinity Fabric interconnect to link separate pieces of silicon ("chiplets") within a single processor package. The multi-chip processor uses 7nm process technology for the "Zen 2" CPU cores that benefit from the advanced process technology, while leveraging a mature 14nm process technology for the input/output portion of the chip. AMD said that the result is much higher performance – more CPU cores at the same power, and more cost-effective manufacture than traditional monolithic chip designs.

Combining this design methodology with the benefits of TSMC’s 7nm process technology, "Zen 2" delivers significant performance, power consumption and density generational improvements that can help reduce datacenter operating costs, carbon footprint and cooling requirements. Other key generational advances over the "Zen" core include:

- An improved execution pipeline, feeding its compute engines more efficiently.

- Front-end advances – improved branch predictor, better instruction pre-fetching, re-optimized instruction cache and larger op cache.

- Floating point enhancements – doubled floating point width to 256-bit and load/store bandwidth, increased dispatch/retire bandwidth and maintained high throughput for all modes.

- Advanced security features – Hardware-enhanced Spectre mitigations, taking software migration and hardening it into the design, and increased flexibility of memory encryption.

As a result, AMD claims its 7nm x86 chips will beat Intel’s 10nm versions — now expected late next year — in both performance as well as time to market. In addition, the company enhanced its Infinity fabric, a cache coherent processor link, although it declined to give details.

Separately, the Zen 2 cores implement in hardware fixes for the Spectre side-channel attacks that AMD had patched in software. The chips were not vulnerable to the Meltdown or Foreshadow attacks, AMD said.

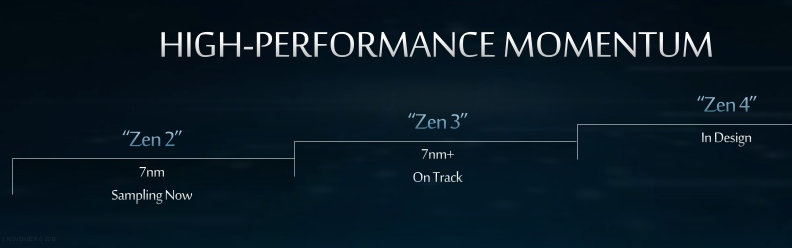

Multiple 7nm-based AMD products are now in development, including next-generation AMD EPYC CPUs and AMD Radeon Instinct GPUs, both of which AMD detailed and demonstrated at the event. Additionally, the company shared that its follow-on 7nm+-based "Zen 3" and "Zen 4" x86 core architectures are on-track. AMD said that the Zen 4 is currently in development.

AMD EPYC Server CPU Updates

AMD also disclosed new details and delivered performance previews of its next-generation EPYC processors codenamed "Rome":

- Processor enhancements including up to 64 "Zen 2" cores (twice as many as the 14nm Naples chip that used first-generation Zen cores), increased instructions-per-cycle and leadership compute, I/O and memory bandwidth. It sports up to 128 lanes of the interconnect compared to 96 lanes of Gen 3 for Intel’s current high-end server chips.

- Platform enhancements including the first PCIe 4.0-capable x86 server processor with double the bandwidth per channel to improve datacenter accelerator performance.

- Double the compute performance per socket and four times the floating point performance per socket compared to current AMD EPYC processors.

- Socket compatibility with today’s AMD EPYC server platforms.

The chips and a next-generation Milan will all fit into the same socket so companies do not have to design new motherboards.

AMD demonstrated the performance and platform advantages of its next-generation EPYC processor with two demos during the event:

- A pre-production single-socket next-generation AMD EPYC processor outperforming a commercially available top-of-the-line Intel dual processor Xeon server running the computationally-intensive, industry standard "C-Ray" benchmark.

- The first x86 PCIe 4.0-capable platform demo, featuring a Radeon Instinct MI60 processor to accelerate image recognition.

Overall, Rome delivers twice the throughput of Naples and four times its floating-point performance, AMD said.

AMD is sampling "Rome" with its customers now and is expected to be the world’s first high-performance x86 7nm CPU.After that, AMD plans to release a processor based on its Zen 3 architecture and these chips will be made using TSMC’s N7+ fabrication process that will take advantage of EUV lithography. Since Zen 4 microarchitecture is still in design phase, chances are that processors on its base will be made using a more advanced node.

AMD implied that the first CPUs based on its Zen 3 microarchitecture will ship in 2020, so it is natural to expect Zen 4 to reach actual products in 2021 or later.