Everspin Releases Design Guide for using 1 Gb STT-MRAM with Xilinx DDR4 FPGA Controller

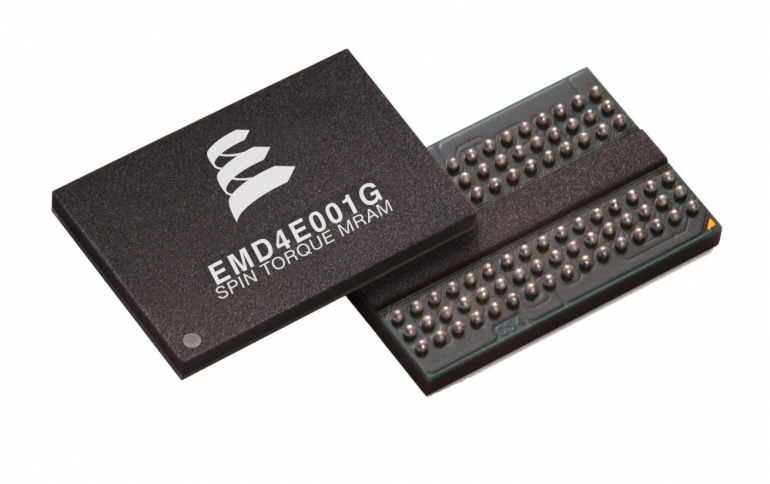

Everspin Technologies, Inc. has released a comprehensive design guide to streamline the integration of its 1 Gigabit (Gb) Spin-transfer Torque Magnetoresistive Random Access Memory (STT-MRAM) product in the storage marketplace.

Xilinx, Inc. has been supporting Everspin’s STT-MRAM for two generations and enables the 1 Gb STT-MRAM solution using its DDR4 controller in the Xilinx Vivado development environment.

The Everspin and Xilinx integrated solution provides benefits, with the design guide and tools structured to address:

- Timing: Reducing operating frequency, increasing row access timing, increasing counter widths and reducing CAS page sizes

- Power-Up: Enabling anti-scribble mode during calibration

- Power-Down: Scramming or moving all relevant data into the persistent memory array

- Performance: Increasing pipeline depth and data transfer efficiency

- Scripts: Providing Verilog models and other detailed information to get storage OEM’s design up and running effectively

Everspin’s STT-MRAM devices are delivering protection against power loss without the use of supercapacitors or batteries. In addition, the larger density 1 Gb part offers more effective management of I/O streams, creating a greater level of latency determinism and allowing storage OEMs to improve quality of service of their products. Similar benefits can also be achieved using the 1 Gb STT-MRAM device as a persistent data write buffer in storage and fabric accelerators, computational storage, and other applications.