Imagination Extends the MIPS Warrior CPU Family

Imagination Technologies has added new chips to its MIPS Warrior CPU product line. The additions include the embedded 32-bit M-class M6200 and M6250 CPUs and high-end P-class P6600 64-bit CPU. The MIPS P6600 is the next evolution of the MIPS P-class family, building on the 32-bit P5600 CPU, and paving the way to future generations of higher performance 64-bit MIPS processors. The P6600 is a balanced mainstream high-performance CPU choice, enabling multicore 64-bit SoCs with area efficiency for applications in segments including mobile, home entertainment, networking, automotive and more.

The MIPS M6200 and M6250 are the latest additions to Imagination’s M-class family processors for MCUs/MPUs for embedded designs in segments requiring higher performance and larger address space, including wired/wireless modems, GPU supervisor processors, flash and SSD controllers, packet processing, industrial and motor control, voice processing and more.

All based on the MIPS Release 6 (r6) architecture.

MIPS P6600 key features

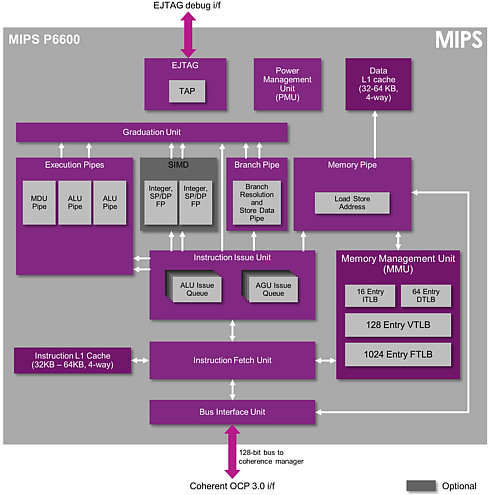

- High-performance 64-bit MIPS Warrior CPU based on a 16-stage multi-issue Out of Order (OoO) pipeline implementation

- Integrated compiler-friendly 128-bit MIPS SIMD Architecture (MSA) support for efficient parallel processing of vector operations in multimedia applications

- Branch prediction with fully associative Level 1 BTB (branch target buffer) and an improved Level 2 cache sub-system

- Full hardware virtualization support and Imagination’s OmniShield technologies for security and reliability in a wide range of applications

Specifications

| Target | TSMC 28HPM |

|---|---|

| Frequency | 1 GHz – 2+ GHz |

| CoreMark/MHz (per core) | > 5 |

| Total CoreMark @ 1.5GHz | > 7500 per core |

| DMIPS/MHz (per core) | 3.5 |

| Total DMIPS @ 1.5GHz | > 5250 per core |

The internal architecture of the MIPS P6600 64-bit CPU

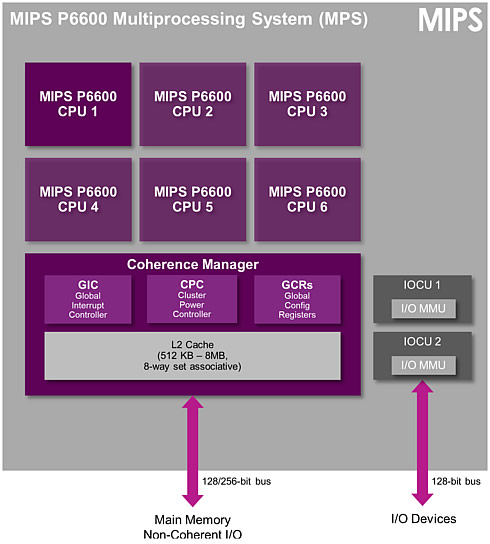

System designers can use this new P-class Warrior CPU in configurations that range from single to hexacore clusters. The figure below shows a block diagram of the MIPS P6600 Multiprocessing System (MPS) that includes a Coherence Manager (CM2) with integrated L2 cache for a more streamlined data flow.

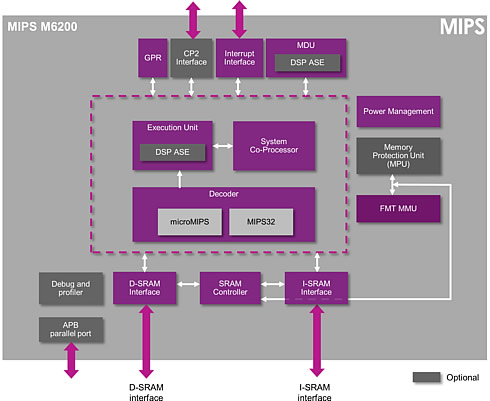

MIPS M6200 MCU & M6250 MPU key features

- Low-power, compact 32-bit CPUs based on a 6-stage pipeline implementation, enabling 30% higher frequencies versus the MIPS microAptiv CPU for similar implementations

- Integrated DSP and SIMD functionality to address signal processing requirements of such applications as industrial/motor control, voice processing and more

- Support for microMIPS r6 Instruction Set Architecture (ISA) for code compression and reduced memory footprint

- Data integrity features, including ECC and parity protection

- AMBA APB debug interface enabling JTAG, multi-core and mixed core debugging

M6200 MCU:

- Includes a memory controller for tightly coupled 64-bit Instruction/Data SRAM

- A memory protection unit enables program/data security

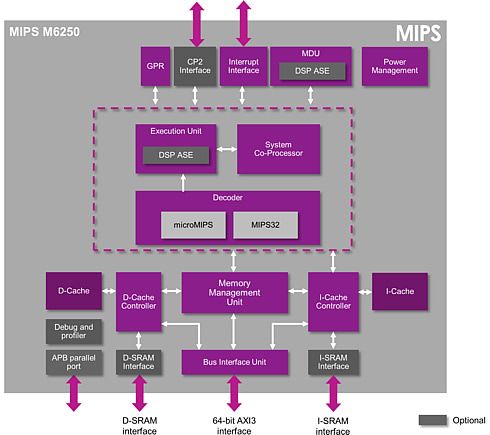

M6250 MPU:

- Includes a memory controller for Instruction/Data L1 cache and optional tightly coupled ScratchPad RAMs (SPRAMs)

- A Memory Management Unit (MMU) supports virtual memory, enabling full support for Linux and other high level operating systems

- 40-bit eXtended Physical Addressing (XPA) support

- AMBA AXI3 Bus Interface Unit

28HPM 12T SVt |

M6200 |

M6250 |

| Freq (MHz) | 750 |

750 |

| Core Area (mm2) | 0.19 |

0.23 |

| Core Power (µW/MHz) | 60 |

62 |

These M-class processors are 6-stage pipeline designs that implement the MIPS32 Release 6 architecture and also include support for the microMIPS32 ISA, a set of optimized 16-bit and 32-bit instructions that provide a reduction in code size with a performance equivalent to MIPS32.

MIPS M6200 is a 32-bit M-class CPU designed for microcontroller and embedded devices that run real-time operating systems; the processor includes an SRAM controller and 64-bit instruction and data SRAM interfaces.

MIPS M6250 is a 32-bit M-class CPU designed for microprocessor devices that require Linux capabilities; it includes a high-speed 64-bit AXI bus interface, a Memory Management Unit (MMU), data and instruction cache controllers, and support for eXtended Memory Addressing (XPA) to 40-bit physical address space (up to 1 TB of system memory).

The M6200, M6250 and P6600 are all available now.