Advances In Semiconductor Technology On Display At The ISSCC

At the International Solid State Circuits Conference (ISSCC), Samsung and TSMC will describe 7nm SRAMs, Mediatek will show a 10nm SoC and STMicroelectronics will unveil a neural network accelerator made in a fully depleted silicon-on-insulator process.

Besides the papers describing the progress in traditional chip scaling, TSMC and Texas Instruments executives will deliver

keynotes that explore emerging ways to advance semiconductors with chip stacks, novel circuit designs and new materials.

Researchers will also give keynote talks on DNA sequencing and quantum computing.

AMD will detail its upcoming Zen x86 core, a quad-core x86 complex with 8 Mbytes L3, presented at Hot Chips earlier this year.

In the same session, Intel will present a paper on the Altera Stratix 10, a GHz-class FPGA with 17 billion transistors made in a 14nm process.

In memories, Samsung and a team from Western Digital (now the parent of Sandisk) and Toshiba will reveal separate 512 Gbit NAND flash designs. Both pack three bits per cell and achieve their density using 64 stacked layers.

The WD/Toshiba part has a 3.88Gb/mm2 areal density and sports a 20% faster read-sensing scheme to improve read throughput over current flash chips. The Samsung device uses a 1.2V I/O voltage supply to increase read bandwidth at lower power. The chips will serve the high end of a solid-state drive market valued at more than $25 billion in 2017, organizers said.

SK Hynix and Toshiba will present a 4Gbit STT-MRAM chip sporting a density of 0.0026mm2 per Mbit. It rides an LPDDR2-compatible interface with a 2.5ns clock cycle and targets low power uses in the Internet of Things.

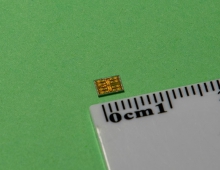

TSMC will unveil what organizers called "the smallest SRAM bit cell published to date." The 0.027μm2 256 Mbit SRAM is made in a 7nm FinFET process using write-assist circuitry for low Vmin applications.

Samsung Electronics will not be far behind with a 7nm FinFET SRAM less than 0.030μm2 in area. The part is made using extreme ultraviolet lithography for peripheral repair analysis, an approach said to improve Vmin by 39.9 mV based on failure analysis.

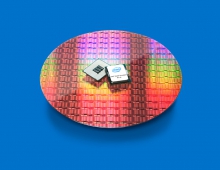

Samsung announced earlier this year it plans to put EUV steppers into production earlier than rivals, in part because it is testing them in both logic and memory fabs. TSMC has said it will wait for 5nm before inserting EUV.

STMicroelectronics will describe a 28nm FD-SOI SoC that delivers 2.9TOPS/W. The 200 MHz chip sports a peak performance on deep convolutional neural network jobs of more than 676 GOPS while running on a 0.575V power supply. The SoC integrates a host CPU, a 16 DSP array and a convolutional deep neural network accelerator.

Mediatek will present a paper on a 10nm, ten-core mobile SoCs. The new SoC sports three clusters of three different types of ARM cores including a Cortex-A73 complex.

The fabless company will also give papers on advanced Bluetooth, LTE-Advanced and Wi-Fi chips.

The ISSCC 2017 will be held February 5-9, 2017, in San Franscisco, CA.