AMD Targets Notebooks and All-in-Ones With 6th Generation A-Series Processor

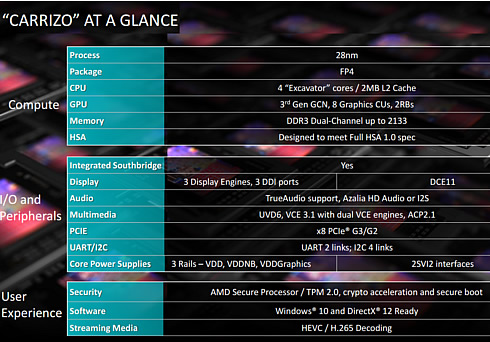

AMD today announced at Computex its 6th Generation A-Series Processor, previously codenamed "Carrizo." WIth the new high-performance Accelerated Processing Unit (APU) that comes in a System-on-Chip (SoC) design, AMD is targetting mainstream notebooks that will have a long battery life. The 6th Generation AMD A-Series Processor takes advantage of AMD processor and graphics IP. The SoC design marks a number of technology firsts: the first High Efficiency Video Coding (HEVC/H.265) hardware decode support for notebooks, the first Heterogeneous Systems Architecture (HSA) 1.0-compliant design, and the first ARM TrustZone-capable high-performance APU.

The 15W focused APU harnesses up to 12 Compute Cores -- 4 CPU + 8 GPU -- leveraging AMD "Excavator" cores and the third generation of AMD's Graphics Core Next (GCN) architecture. This means that the fundamental design behind the cores, the caches and the libraries have all changed.

Carrizo will be made at the 28nm node. The new FP4 package will be used, but this will be shared with Carrizo-L, which will come sometime later this year. All Carrizo APUs currently have four Excavator cores, more commonly referred to as a dual module design, and as a result the overall design will have 2MB of L2 cache.

Carrizo integrates the southbridge/IO hub into the silicon design of the die itself, rather than a separate on package design. This brings the southbridge down from 40nm+ to 28nm, saving power and reducing long distance wires between the processor and the IO hub. This also allows the CPU to control the voltage and frequency of the southbridge more than before, offering further potential power saving improvements.

One of the biggest changes in the design is the increase in the L1 data cache, doubling its size from 64 KB to 128 KB while keeping the same efficiency. This is combined with a better prefetch pipeline and branch prediction to reduce the level of cache misses in the design.

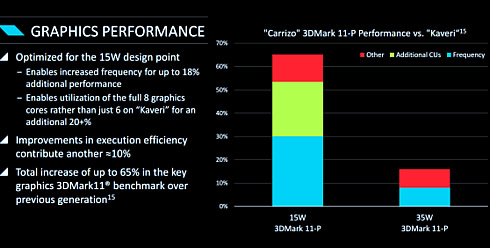

Another big upgrade in graphics for Carrizo is that the maximum number of compute units for a 15W mobile APU moves up from six (384 SPs) to eight (512 SPs), affording a 33% potential improvement. This means that the high end A10 Carrizo mobile APUs will align with the A10 Kaveri desktop APUs, although the desktop APUs will use 6x the power.

Carrizo also moves to AMD’s third generation of Graphics Core Next, with up to 512 streaming processors in the top end design. It will also feature dual channel DDR3-2133 memory. This is similar to the R9 285 retail graphics cards and gives DirectX 12 support.

External graphics is supported by a PCIe 3.0 x8 interface, and the system relies on three main rails for voltage across the SoC which allows for separate voltage binning of each of the parts. Carrizo will also support three displays. TrueAudio is also present.

When it comes to power, Carrizo uses low power states, and the different frequency domains within the SoC. Carrizo has ten power planes that can be controlled at run-time, allowing for what can be described as a dynamic race to sleep. This is bundled with access to the S0i3 power state, giving sub 50mW SoC power draw when in sleep and wake-up times under a second.

This is also combined with automated voltage/frequency sensors, of which an Excavator core has 10 each. These sensors take into consideration the instructions being processed, the temperature of the SoC, the quality of power delivery as well as the voltage and frequency at that point in order to relay information about how the system should adjust for the optimal power or performance point.

Last but not least, the Carrizzo supports the voltage adaptive operation that was introduced back in Kaveri. In a few words, the the system will reduce the frequency and the voltage of the processor by around 5% in cases when the voltage that supplies the APU drops below a threshold value (Voltage Droop). Although the work being done in the APU will slow down, the chip will not drain in terms of power.

AMD says that this happens in as quickly as 3 cycles from detection, or in under a nanosecond. When the voltage drop is normalized, the frequency is cranked back up and work can continue at a normal rate.

All the performance metrics rolled in, and AMD is quoting a 65% performance improvement at 15W compared to Kaveri.

For 10Mbps 1080p HEVC content, AMD is stating 300 minutes of unplugged playback time on Carrizo compared to 112 minutes with Kaveri. In a similar test using the same equipment above and the H264 clip of Big Buck Bunny, AMD showed a 8.3 hours playback for Carrizo against 3.3 hours with Kaveri. This is mainly due to teh fact that the UVD now has 4x the bandwidth, allowing 1080p frames to be decoded in 1/4 of the time.

At Computex, AMD provided results comparing their 15W APUs to some of Intel's 15W CPUs, and in those results the 15W APUs compare favorably. The Intel parts are HD 5500 graphics, with 24 execution units (the i3 has 23). It is worth noting that Intel also offers 15W SKUs with the higher-frequency 24EU HD 6000, so the HD 5500 AMD is comparing themselves against is not Intel's most powerful iGPU.

The chips also enable the latest Windows 10 features with Secure boot and resume, Trusted Platform Module (TPM 2.0), and Drive Key Encryption using the first AMD Secure Processor for performance APUs.

Carrizo also comes with security though a built in a single 32-bit Cortex-A5 processor into the die. This divides out memory and processing to allow a complete secure ARM TrustZone element separate from the main CPU cores and memory.

In addition, the new APUs support AMD Gesture Control. Available on mainstream notebooks, it will allow users to navigate and control their notebook with a simple wave of the hand.

AMD mentioned that the FX-8800P, A10-8700P and A8-8600P APUs will find their way to motebooks starting in June.

New 'Fiji' GPU To launch June 16th

AMD has confirmed at Computex that they’ll be revealing their forthcoming high-end video card in a press event on June 16.

The company will be hosting an event on June 16th at 9am PST to release the details on the card, in a presentation dubbed "AMD Presents: The New Era of PC Gaming." The presentation will be taking place at the Belasco Theater in Los Angeles, CA during E3 week.

The company will be hosting an event on June 16th at 9am PST to release the details on the card, in a presentation dubbed "AMD Presents: The New Era of PC Gaming." The presentation will be taking place at the Belasco Theater in Los Angeles, CA during E3 week.

On stage of Computex, AMD CEO Lisa Su showed a chip for technology called HBM (high-bandwidth memory), which could make graphics chips faster and more power-efficient.

HBM offers 3.5 times the bandwidth per watt of GDDR5, which is currently used in memory chips. Instead of being placed next to each other, HBM stacks memory chips, which are connected through a high-speed thread. HBM is also faster due a wider bus and its closer location to graphics processors.

The new memory technology could also help shrink the size of GPUs, or add more memory in the same area. About 1GB of HBM memory takes up 95 percent less than the same amount of GDDR5 memory, so you free up a lot of room on a circuit board, said Robert Hallock, technical marketing manager at AMD.

The company’s graphics rival Nvidia is developing similar stacked memory technology that will appear next year in GPUs code-named Pascal.

FreeSync-over-HDMI

AMD had demoed a FreeSync proof-of-concept laptop demo back at CES 2014 and later FreeSync was implement into the DisplayPort standard as DisplayPort Adaptive-Sync (DPAS). The first FreeSync monitors equipped DisplayPort ports (not HDMI) were shipped back in March of this year.

The company demonstrated a prototype implementation of FreeSync-over-HDMI at their suite at Computex 2015.

AMD's windmill FreeSync demo was running in a system powered by an R9 200 series card, and the result was on display in a prototype FreeSync-enabled HDMI monitor.

The prototype monitor used a Realtek Timing Controller Board (TCON) to control logic signal of gate and source for driving the LCD. The TCON had a custom firmware installed in order to support variable refresh operation and the FreeSync-over-HDMI technology. But since the necessary functionality doesn't currently exist in HDMI, AMD was driving the signal using a custom protocol over HDMI 1.4a.

AMD wants to introduce variable refresh support into the HDMI standard, making it widely available to users, since the majority of monitors out there come with HDMI ports.

Along with the FreeSync-over-HDMI demo, AMD also had one bit of FreeSync news at Computex. As regular readers are likely aware, all of the current DPAS monitors have a minimum refresh rate over 30Hz – typically 40Hz or 48Hz – which unfortunately for AMD’s FreeSync efforts is counterproductive to their goals since you lose the bulk of the benefits of FreeSync when framerates fall below the minimum refresh rate. And although this is a monitor limitation rather than a DPAS/FreeSync limitation, AMD is still looking to push vendors to get lower minimum rate monitors on the market and to promote those monitors.

Vendor Nixeus has announced the first 30hz minimum refresh rate DPAS monitor, the NX-VUE24. The NX-VUE24 is a 24", 1080p TN display that supports variable refresh rates from 30Hz up to 144Hz. As a note, all of the current DPAS monitors have a minimum refresh rate over 30Hz, and cannot support AMD’s FreeSync.

Nixeus has not yet announced a release date or price for the monitor.